digital

langar

MOS

**Applications**

NUMERICAL INDEX FUNCTIONAL INDEX

> INTERFACE APPLICATIONS

MSI APPLICATIONS

ECL APPLICATIONS

are in section 5 (purple)

LINEAR APPLICATIONS

MOS APPLICATIONS

AL INDEX AL INDEX

2

3

4

5

6

7

#### Copyright 1974

#### SIGNETICS CORPORATION

Signetics Corporation reserves the right to make changes in the pducts contained in this book in order to improve design or performance and to supply the best pasible product.

Signetics Corporation assumes no responsibility for the use of ancircuits described herein and makes no representations that they are free from patent infringeent.

Only the following product lines will be made evailable for mility applications (i.e., applications requiring full militery temperature range end/or specifications over than those on the device data sheets).

54 series

54S series

82 series (except es noted on the data sheet)

82S series (except es noted on the deta sheet)

8T series (except as noted on the data sheet)

Bipolar Memories: 82S06, 82S07

Linear devices will generally be available in militery temperaturrange but such availability will be limited to ceramic DIP and T-05/T-03 can package configuraties. Linear devices will not be available to environmental specifications other than Signetics standal production screening tests.

Your local Signetics representative will be happy to provide infimation on alternate devices and/or sources for discontinued military product types.

# STOPPE TO THE

NUMERICAL INDEX FUNCTIONAL INDEX

## **Numerical Index and Table of Contents**

| 02091          | Asynchronous Presettable Mol Counter/Storage Element                                                      | 3-                     |

|----------------|-----------------------------------------------------------------------------------------------------------|------------------------|

| 82S90<br>82S91 | Asynchronous Presettable MSI Counter/Storage Element Asynchronous Presettable MSI Counter/Storage Element | 3-7<br>3-7             |

| 8293           | Presettable Low Power Binary Counter                                                                      | 3-7                    |

| 8292           | Presettable Low Power Decade Counter                                                                      | 3-7                    |

| 8291           | Presettable High Speed Binary Counter                                                                     | 3-7                    |

| 8288<br>8290   | Divide-by-Twelve Counter Presettable High Speed Decade Counter                                            | 3-7                    |

| 8285           | Decade Up/Down Counter                                                                                    | 3-7<br>3-7             |

| 8284           | Binary Up/Down Counter                                                                                    | 3-6                    |

| 8281           | Presettable Binary Counter                                                                                | 3-7                    |

| 8280           | Presettable Decade Counter                                                                                | 3-7                    |

| 8276           | 8-Bit Shift Register                                                                                      | 3-1                    |

| 8275           | Quad Bistable Latch                                                                                       | 3-1                    |

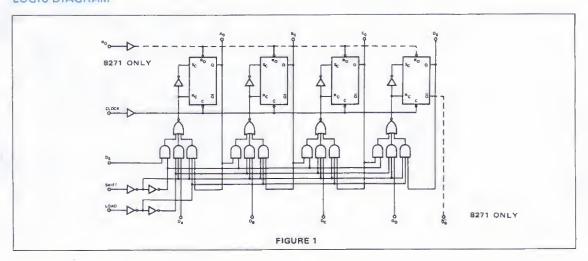

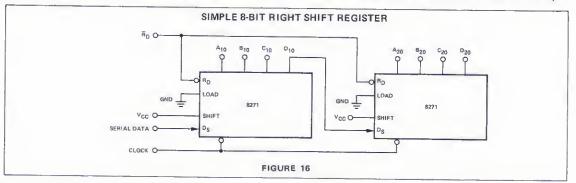

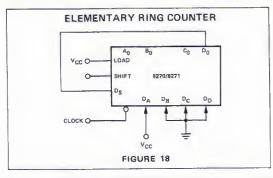

| 8271           | 4-Bit Shift Register                                                                                      | 3-1                    |

| 8270           | 4-Bit Shift Register                                                                                      | 3-1                    |

| 8268           | Gated Full Adder                                                                                          | 3-6                    |

| 8267           | 2-Input 4-Bit Digital Multiplexer                                                                         | 3-2                    |

| 8262<br>8266   | 9-Bit Parity Generator and Checker 2-Input 4-Bit Digital Multiplexer                                      | 3-6<br>3-2             |

| 8261           | Fast Carry Extender                                                                                       | 3-5                    |

| 8260           | Arithmetic Logic Element                                                                                  | 3-5                    |

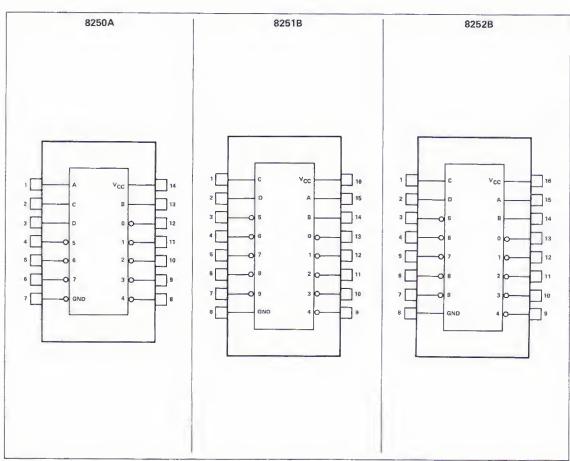

| 8252           | BCD-to-Decimal Decoder                                                                                    | 3-4                    |

| 8251           | BCD-to-Decimal Decoder                                                                                    | 3.4                    |

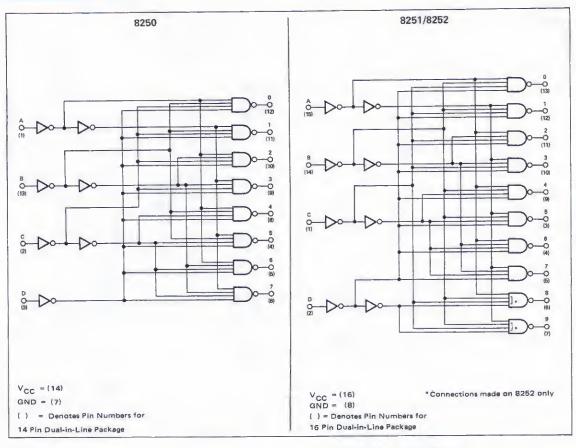

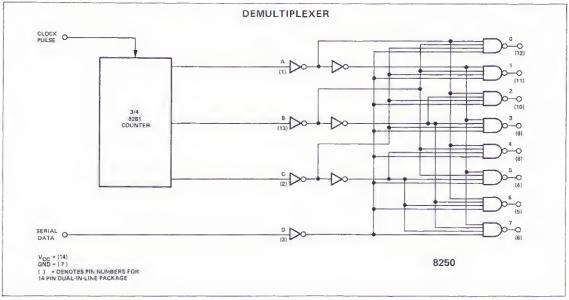

| 8250           | Binary-to-Octal Decoder                                                                                   | 3-4                    |

| 8243           | 8-Bit Position Scaler                                                                                     | 3-3                    |

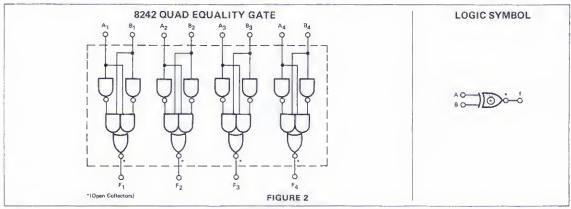

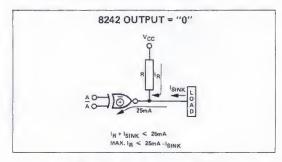

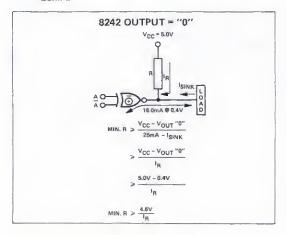

| 8242           | Quad Exclusive NOR                                                                                        | 3-2                    |

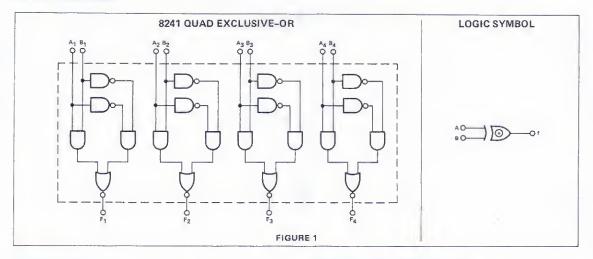

| 8241           | Quad Exclusive OR                                                                                         | 3-2                    |

| 8235           | 2-Input 4-Bit Digital Multiplexer                                                                         | 3-2                    |

| 8234           | 2-Input 4-Bit Digital Multiplexer                                                                         | 3-2                    |

| 8233           | 2-Input 4-Bit Digital Multiplexer                                                                         | 3-2                    |

| 8232           | 8-Input Digital Multiplexer                                                                               | 3-1                    |

| 8231           | 8-Input Digital Multiplexer                                                                               | 3-1                    |

| 8230           | 8-Input Digital Multiplexer                                                                               | 3-1                    |

| 8203           | 10-Bit Buffer Register with D Complement                                                                  | 3-1                    |

| 8202           | 10-Bit Buffer Register                                                                                    | 3-1                    |

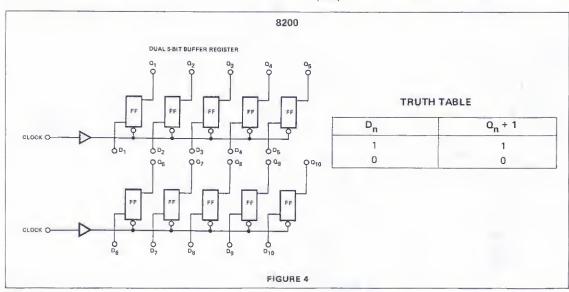

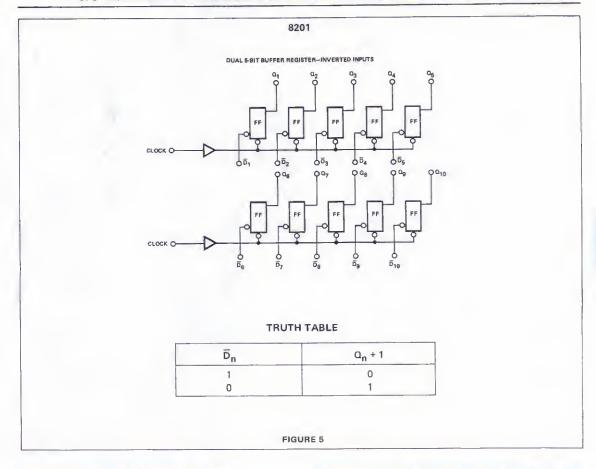

| 8200<br>8201   | Dual 5-Bit Buffer Register  Dual 5-Bit Buffer Register with D Complement                                  | 3-1<br>3-1             |

|                | Dual 5-Rit Ruffer Register                                                                                | 3-1                    |

| 8200 MSI       |                                                                                                           |                        |

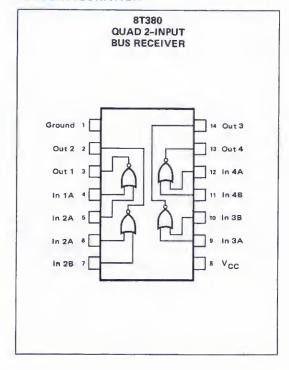

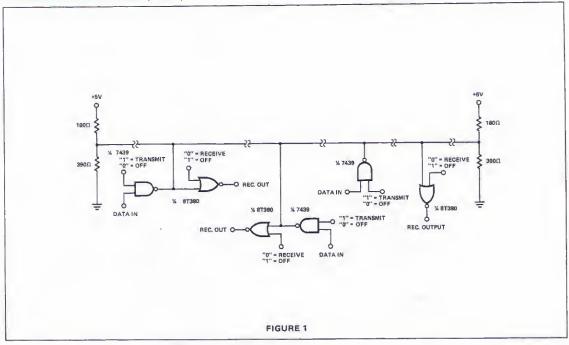

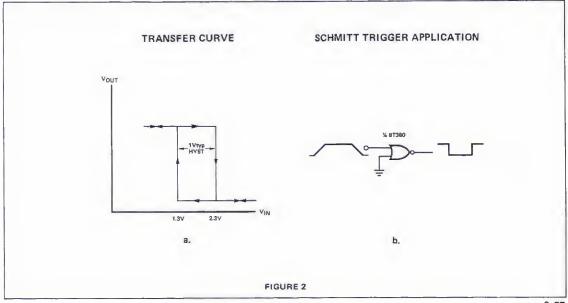

| 8T380          | Quad Bus Receiver with Hysterisis/Schmitt Trigger                                                         | 2-8                    |

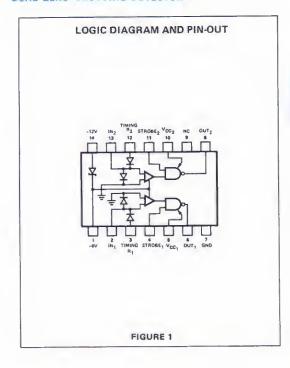

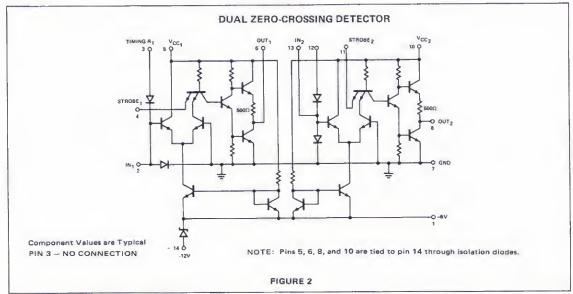

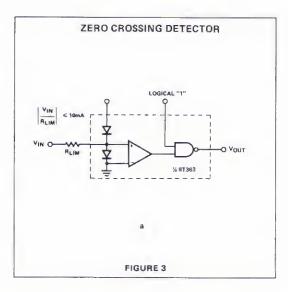

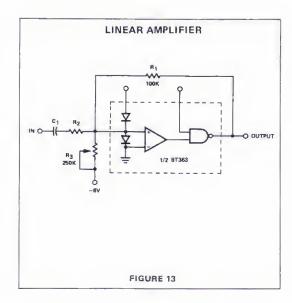

| BT363          | Dual Zero-Crossing Detector                                                                               | 2-7                    |

| BT18           | Interface Element                                                                                         | 2-6                    |

| BT90           | Interface Element (TTL to High Voltage)                                                                   | 2-6                    |

| 3T80           | Interface Element (TTL to High Voltage)                                                                   | 2-6                    |

| 3T26           | Quad Bus Driver/Receiver                                                                                  | 2-6                    |

| BT25           | Dual Sense Amplifier/Latch                                                                                | 2-5                    |

| BT24           | Line Receiver                                                                                             | 2-5                    |

| 3T23           | Line Driver                                                                                               | 2 <del>-4</del><br>2-5 |

| BT22           | Retriggerable Monostable Multivibrator                                                                    | 2-3<br>2-4             |

| 8T16<br>8T20   | Bi-Directional One-Shot                                                                                   | 2-3<br>2-3             |

| 8T15           | Line Driver Line Receiver                                                                                 | 2-3<br>2-3             |

| BT14           | Schmitt Trigger                                                                                           | 2-2                    |

| BT14           | Line Receiver                                                                                             | 2-2                    |

| BT13           | Line Driver                                                                                               | 2-2                    |

| 3T10           | Quad D-Type Bus Flip Flop                                                                                 | 2-1                    |

| 3T09           | Quad Bus Driver                                                                                           | 2-1                    |

| BT06           | Seven Segment Decoder/Driver                                                                              | 2-6                    |

| 3T05           | Seven Segment Decoder/Driver                                                                              | 2-6                    |

|                |                                                                                                           |                        |

| BT04           | Seven Segment Decoder/Driver                                                                              | 2-6                    |

| ECL 10,000        |                                                            |      |

|-------------------|------------------------------------------------------------|------|

| 10124             | Quad Differential Line Driver/Quad TTL to ECL Translator   | 5-1  |

| 10125             | Quad Differential Line Receiver/Quad ECL to TTL Translator | 5-1  |

| LINEAR            |                                                            |      |

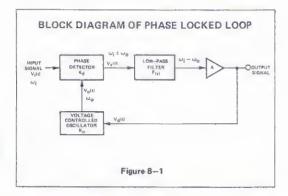

| PLL               | Phase Locked Loop Introduction                             | 6-1  |

| PLL               | Terminology                                                | 6-3  |

| PLL               | Principle                                                  | 6-5  |

| PLL               | Building Blocks                                            | 6-9  |

| PLL               | Functional Applications                                    | 6-12 |

| PLL               | General Loop Setup and Tradeoffs                           | 6-15 |

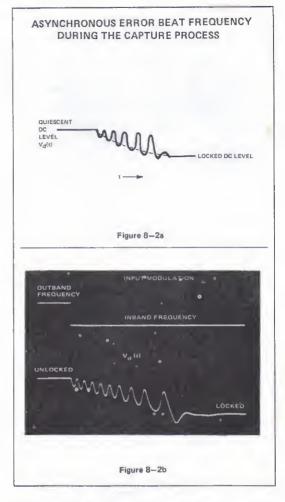

| PLL               | Measurement Techniques                                     | 6-18 |

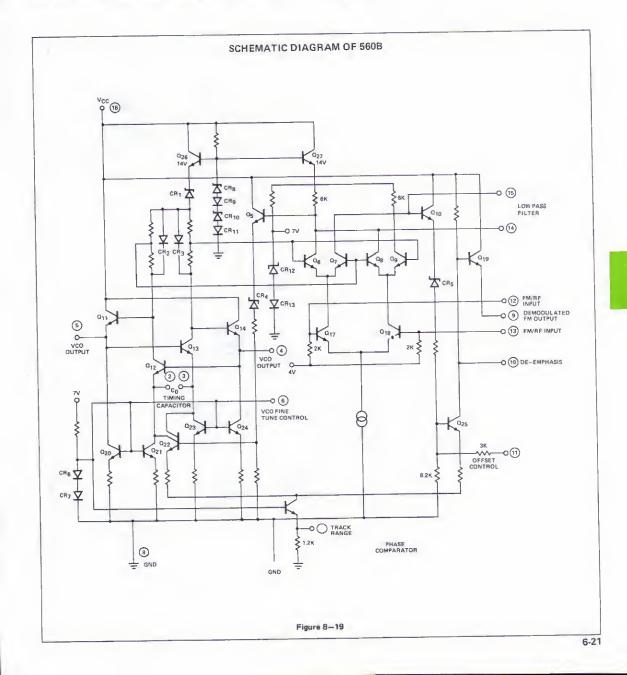

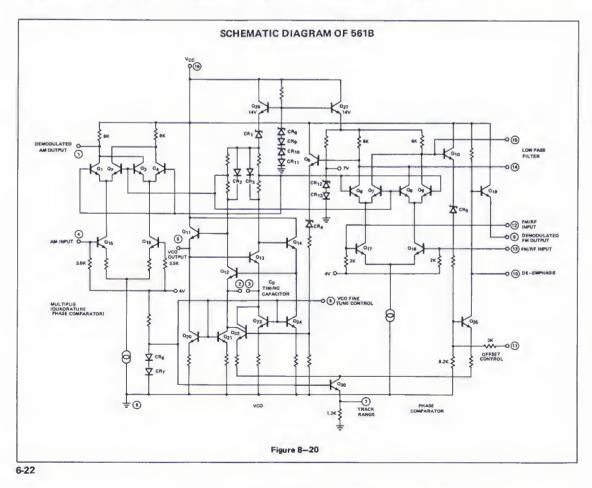

| PLL               | Monolithic Phase Locked Loops                              | 6-22 |

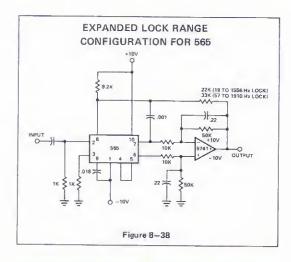

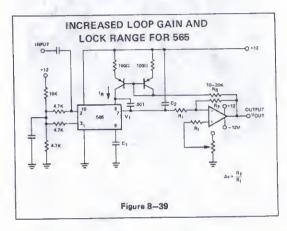

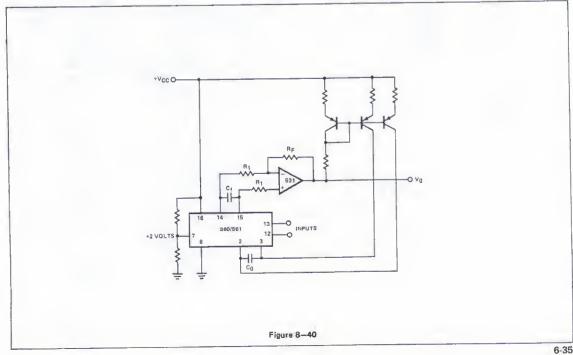

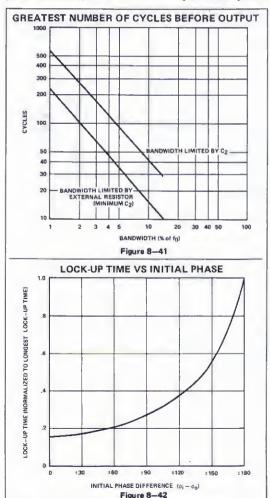

| PLL               | Expanding Loop Capability                                  | 6-34 |

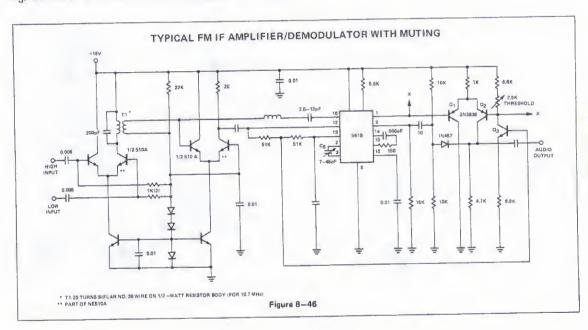

| PLL               | FM IF Amplifier/Demodulator with Muting                    | 6-41 |

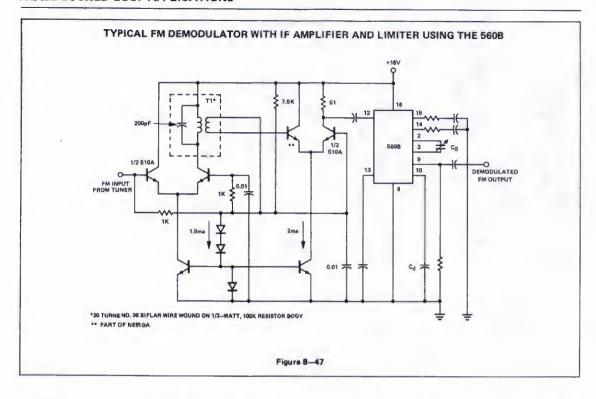

| PLL               | FM Demodulator                                             | 6-41 |

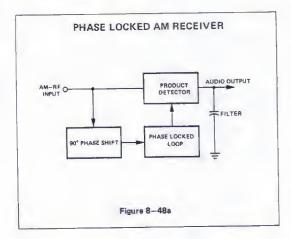

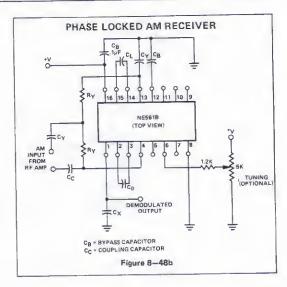

| PLL               | AM Receiver                                                | 6-43 |

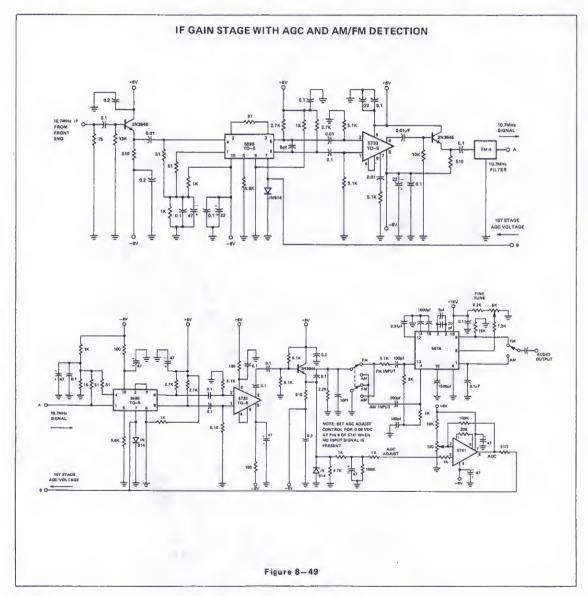

| PLL               | IF Stage with AGC and AM/FM Detection                      | 6-44 |

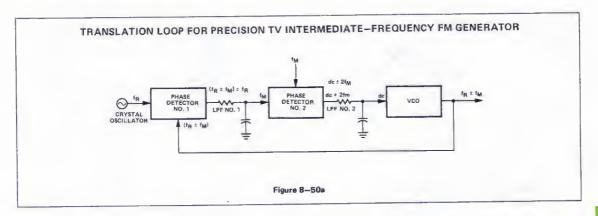

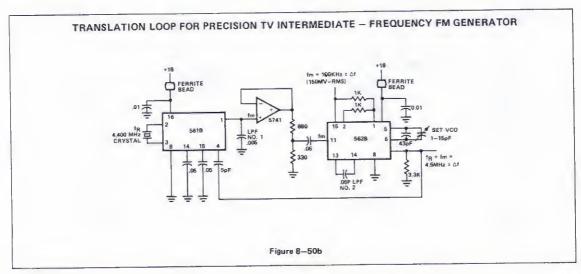

| PLL               | Translation Loop for Precise FM                            | 6-45 |

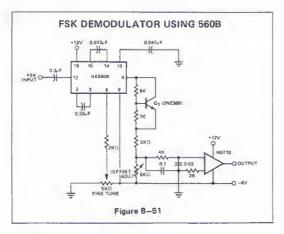

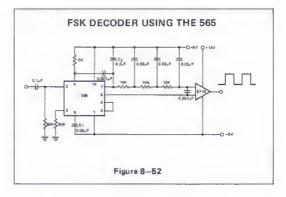

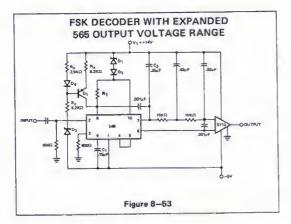

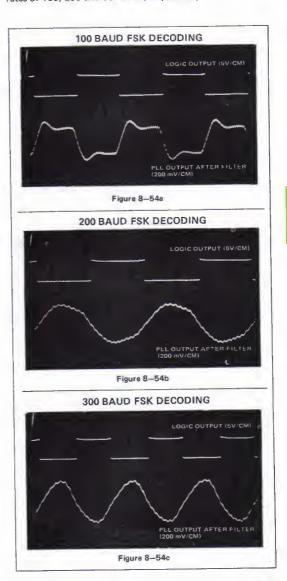

| PLL               | FSK Demodulators                                           | 6-46 |

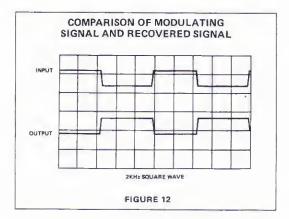

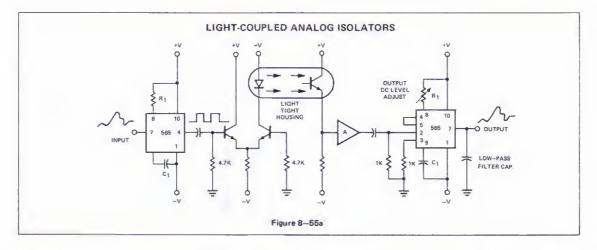

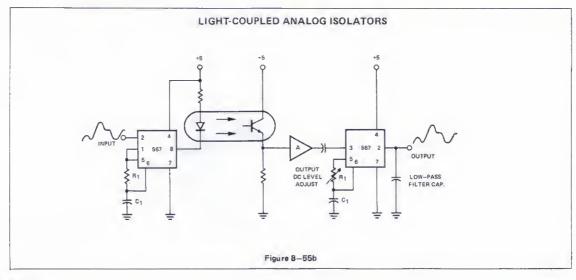

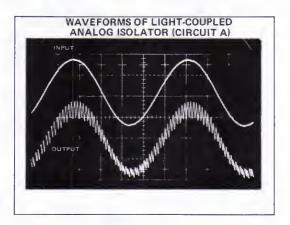

| PLL               | Analog Light-Coupled Isolators                             | 6-48 |

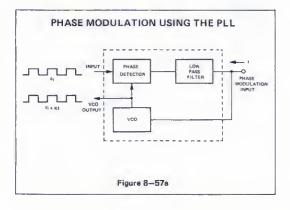

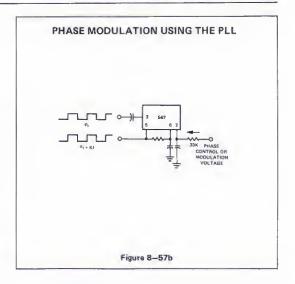

| PLL               | Phase Modulators                                           | 6-49 |

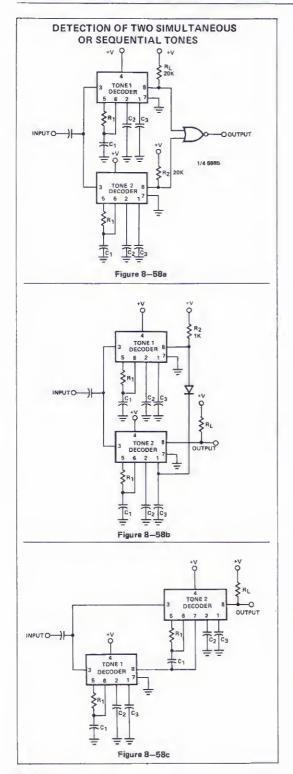

| PLL               | Dual Tone Decoders                                         | 6-49 |

| PLL               | High Speed, Narrow Band Tone Decoder                       | 6-49 |

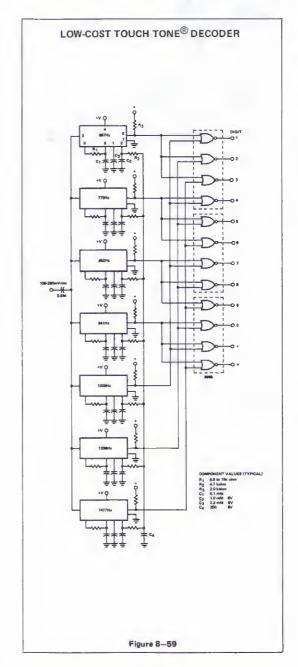

| PLL               | Touch-Tone® Decoder                                        | 6-50 |

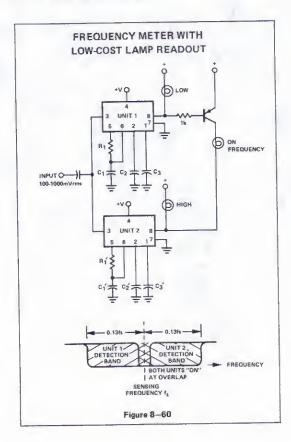

| PLL               | Low Cost Frequency Indicator                               | 6-51 |

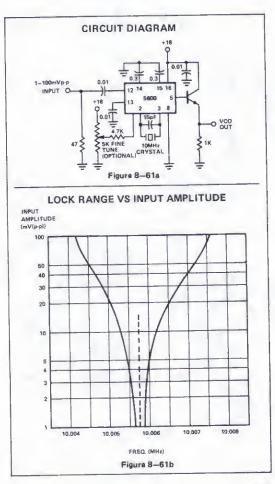

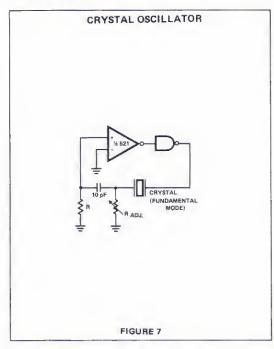

| PLL               | Crystal Stabilized                                         | 6-51 |

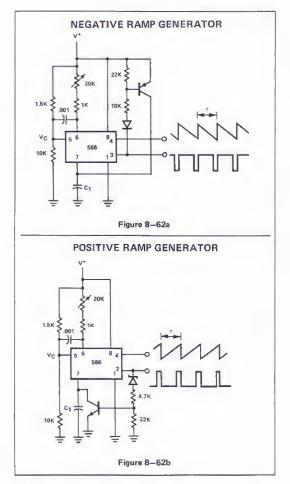

| PLL               | Ramp Generators                                            | 6-52 |

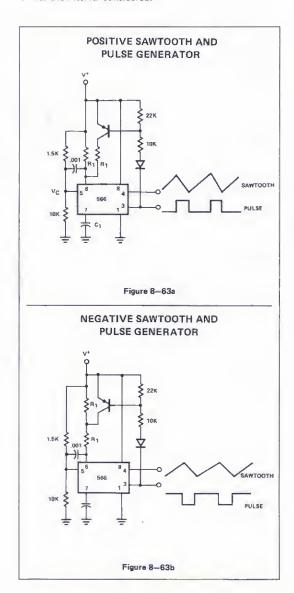

| PLL               | Sawtooth and Pulse Generators                              | 6-52 |

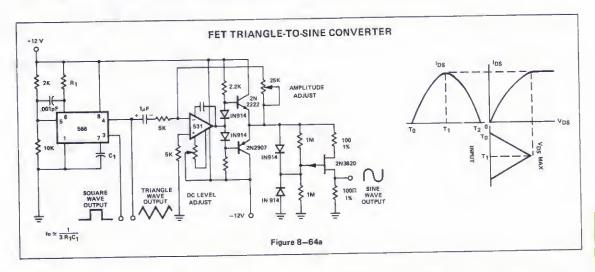

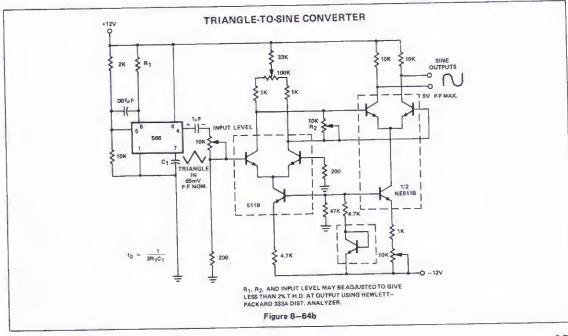

| PLL               | Triangle-to-Sine Converters                                | 6-53 |

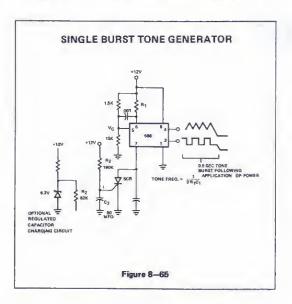

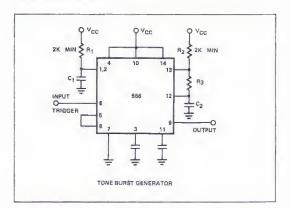

| PLL               | Single Tone Burst Generator                                | 6-54 |

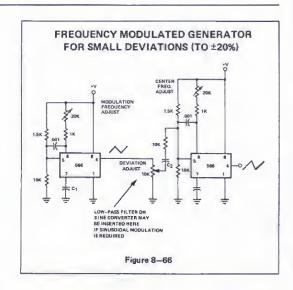

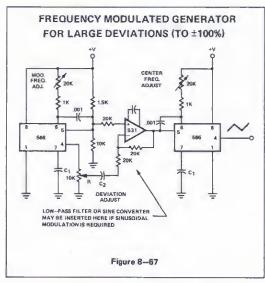

| PLL               | Low Frequency FM Generators                                | 6-54 |

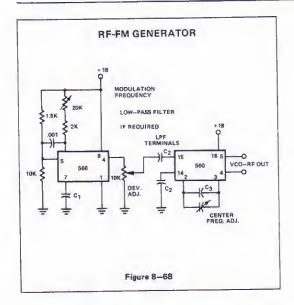

| PLL               | RF-FM Generators                                           | 6-54 |

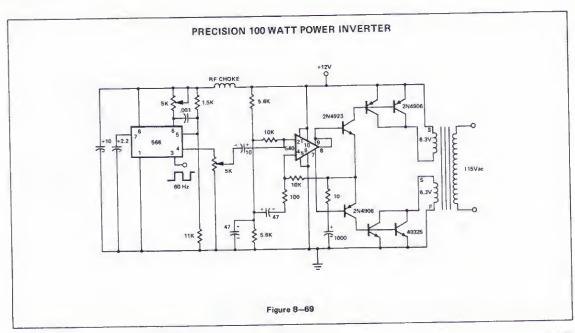

| PLL               | Precision Power Inverter                                   | 6-55 |

| PLL               | Design Ideas                                               | 6-55 |

| PLL               | References                                                 | 6-66 |

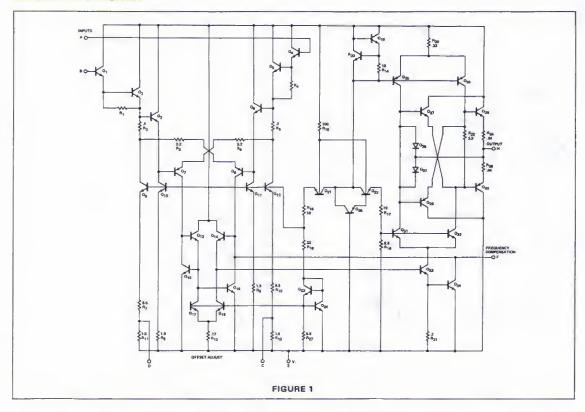

| 521               | High Speed Dual Differential Comparator/Sense Amp          | 6-67 |

| 522               | High Speed Dual Differential Comparator/Sense Amp          | 6-67 |

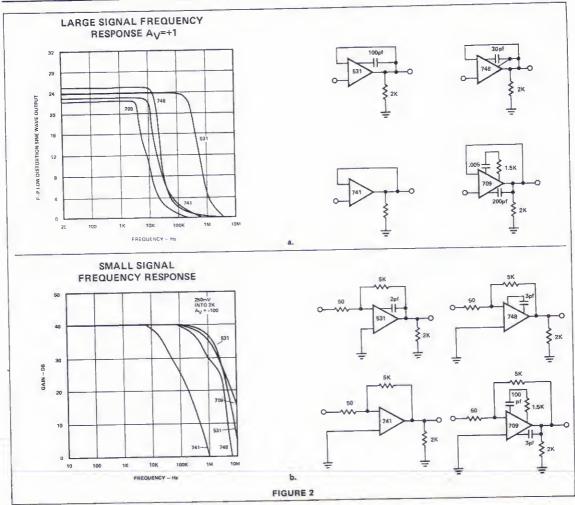

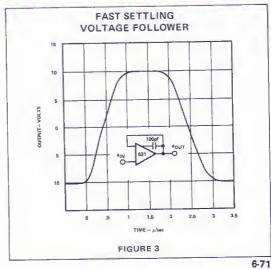

| 531               | High Slew Rate Operational Amplifier                       | 6-73 |

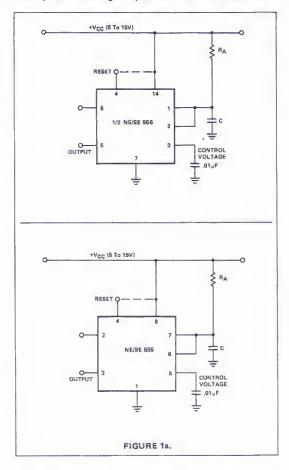

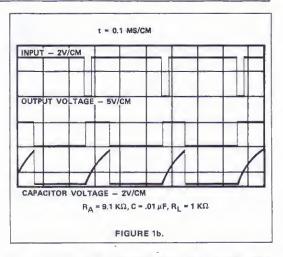

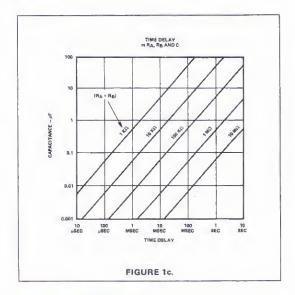

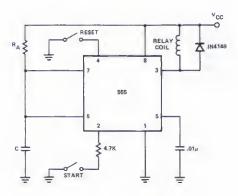

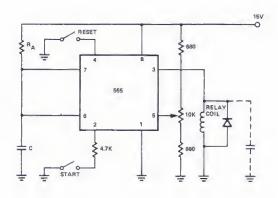

| 555               | Timer                                                      | 6-79 |

| MOS               |                                                            |      |

| 2526              | Read Only Memory                                           | 7-1  |

| 2548-1            | Fully Decoded, 2048-Bit Random Access Memory               | 7-5  |

| 2602              | Fully Decoded 1024-Bit Static Random Access Memory         | 7-12 |

| SALES OFFICE LIST |                                                            | 8-1  |

8-1

## **Functional Index and Table of Contents**

| Product No.   | Name                                                 | Product Line | Page No. |

|---------------|------------------------------------------------------|--------------|----------|

| ARITHMETIC EL | EMENTS                                               |              |          |

|               | Quad Exclusive OR                                    | MSI/TTL 8000 | 3-28     |

| 8241          |                                                      | MSI/TTL 8000 | 3-28     |

| 8242          | Quad Exclusive NOR                                   |              |          |

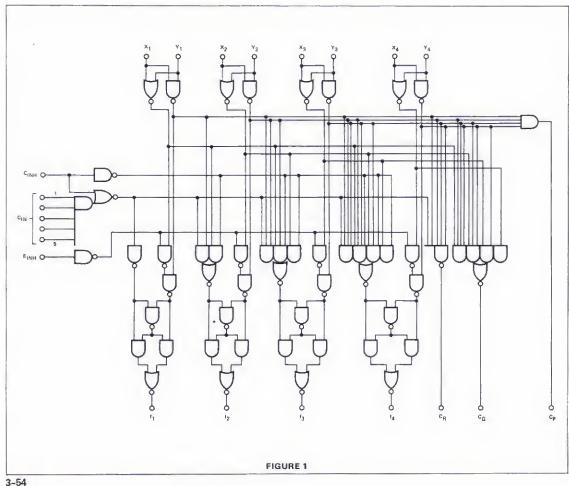

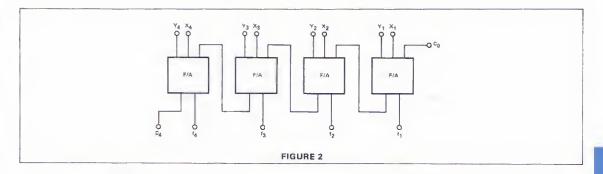

| 8260          | Arithmetic Logic Element                             | MSI/TTL 8000 | 3-54     |

| 8261          | Fast Carry Extender                                  | MSI/TTL 8000 | 3-54     |

| 8262          | 9-8it Parity Generator Checker                       | MSI/TTL 8000 | 3-63     |

| 8268          | Gated Full Adder                                     | MSI/TTL 8000 | 3-66     |

| COUNTERS      |                                                      |              |          |

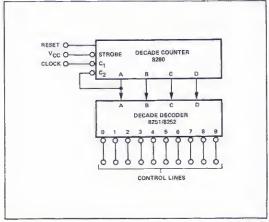

| 8280          | Presettable Decade Counter                           | MSI/TTL 8000 | 3-71     |

| 8281          | Presettable Binary Counter                           | MSI/TTL 8000 | 3-71     |

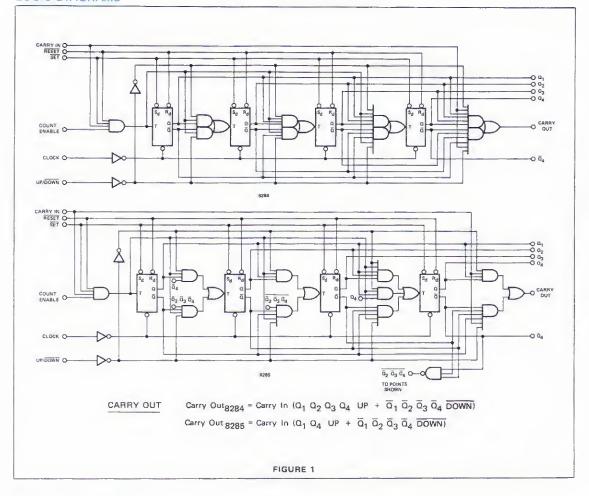

| 8284          | Binary Up/Down Counter                               | MSI/TTL 8000 | 3-88     |

| 8285          | Decade Up/Down Counter                               | MSI/TTL 8000 | 3-88     |

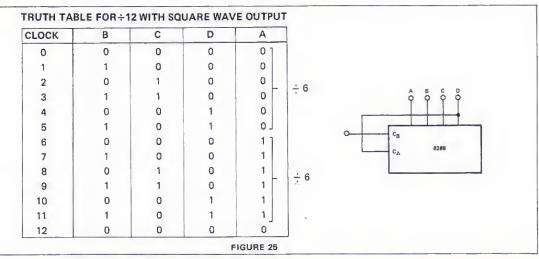

| 8288          | Divide-By-Twelve Counter                             | MSI/TTL 8000 | 3-70     |

| 8290          | Presettable High Speed Decade Counter                | MSI/TTL 8000 | 3-70     |

|               | - ·                                                  | MSI/TTL 8000 | 3-70     |

| 8291          | Presettable High Speed Binary Counter                | MSI/TTL 8000 |          |

| 8292          | Presettable Low Power Decade Counter                 |              | 3-70     |

| 8293          | Presettable Low Power Binary Counter                 | MSI/TTL 8000 | 3-70     |

| 82S90         | Asynchronous Presettable MSI Counter/Storage         | MSI/TTL 8000 | 3-70     |

|               | Element                                              |              |          |

| 82S91         | Asynchronous Presettable MSI Counter/Storage Element | MSI/TTL 8000 | 3-70     |

|               | Element                                              |              |          |

| COMPARATORS   | AND SENSE AMPLIFIERS                                 |              |          |

| 521           | High Speed Dual Differential Comparator/Sense Amp    | Linear       | 6-73     |

| 522           | High Speed Dual Differential Comparator/Sense Amp    | Linear       | 6-67     |

| 531           | High Slew Rate Operational Amplifier                 | Linear       | 6-71     |

| 25000500/201  | MEDO                                                 |              |          |

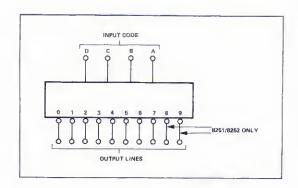

| DECODERS/DRI  |                                                      | MSI/TTL 8000 | 3-48     |

| 8250          | 8inary-to-Octal Decoder                              |              | 3-48     |

| 8251          | 8CD-to-Decimal Decoder                               | MSI/TTL 8000 | 3-48     |

| 8252          | 8CD-to-Decimel Decoder                               | MSI/TTL 8000 |          |

| 8T01          | Nixie* Decoder/Driver                                | MSI/TTL 8000 | 2-1      |

| 8T04          | Seven Segment Decoder/Driver                         | MSI/TTL 8000 | 2-6      |

| 8T05          | Seven Segment Decoder/Driver                         | MSI/TTL 8000 | 2-6      |

| 8T06          | Seven Segment Decoder/Driver                         | MSI/TTL 8000 | 2-6      |

| LATCHES       |                                                      |              |          |

| 8275          | Quad Bistable Latch                                  | MSI/TTL 8000 | 3-1      |

|               |                                                      |              |          |

| INTERFACE ELE |                                                      | MCI/TTI 0000 | 2-1      |

| 8T01          | Nixie* Decoder/Driver                                | MSI/TTL 8000 |          |

| 8T04          | Seven Segment Decoder/Driver                         | MSI/TTL 8000 | 2-6      |

| 8T05          | Seven Segment Decoder/Driver                         | MSI/TTL 8000 | 2-6      |

| 8T06          | Seven Segment Decoder/Driver                         | MSI/TTL 8000 | 2-6      |

| 8T09          | Quad 8us Driver                                      | MSI/TTL 8000 | 2-16     |

| 8T10          | Quad D-Type Bus Flip Flop                            | MSI/TTL 8000 | 2-16     |

| 8T13          | Line Driver                                          | MSI/TTL 8000 | 2-22     |

| 8T14          | Line Receiver                                        | MSI/TTL 8000 | 2-22     |

| 8T14          | Schmitt Trigger                                      | MSI/TTL 8000 | 2-28     |

| 8T15          | Line Driver                                          | MSI/TTL 8000 | 2-30     |

| 8T16          | Line Receiver                                        | MSI/TTL 8000 | 2-30     |

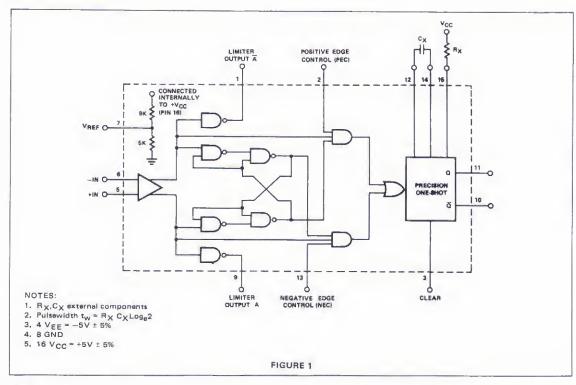

| 8T20          | 8i-Directional One-Shot                              | MSI/TTL 8000 | 2-36     |

| 8T22          | Retriggerable Monostable Multivibrator               | MSI/TTL 8000 | 2-46     |

| 8T23          | Line Driver                                          | MSI/TTL 8000 | 2-54     |

| 8T24          | Line Receiver                                        | MSI/TTL 8000 | 2-54     |

| 8T25          | Dual Sense Amplifier/Letch                           | MSI/TTL 8000 | 2-58     |

| 8T26          | Qued 8us Driver/Receiver                             | MSI/TTL 8000 | 2-62     |

| 8T80          | Interfece Element (TTL to High Voltage)              | MSI/TTL 8000 | 2-67     |

| 8T90          | Interface Element (TTL to High Voltage)              | MSI/TTL 8000 | 2-67     |

| 8T18          | Interface Element (High Voltage to TTL)              | MSI/TTL 8000 | 2-67     |

| 8T363         | Duel Zero-Crossing Detector                          | MSI/TTL 8000 | 2-75     |

| 8T380         | Quad Bus Receiver with Hysterisis/Schmitt Trigger    | MSI/TTL 8000 | 2-81     |

| 0.000         |                                                      | ,            |          |

| INTERFACE ELE  | MENTS (Continued)                                              |                              |              |

|----------------|----------------------------------------------------------------|------------------------------|--------------|

| 10124          | Quad Differential Line Driver/Quad TTL to ECL                  | ECL                          | 5-1          |

| 10125          | Translator                                                     |                              |              |

| 10125          | Quad Differential Line Receiver/Quad ECL to TTL<br>Translator  | ECL                          | 5-1          |

| MEMORIES       |                                                                |                              |              |

| 82S06/07/16/17 | 256-Bit Bipolar Random Access Storage Element                  | Bipolar Memory               | 4.1          |

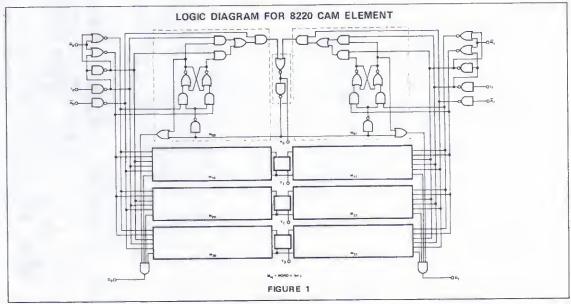

| 8220           | Content Addressable Memory                                     | Bipolar Memory               | 4-1<br>4-7   |

| 2526           | Read Only Memory                                               | MOS                          | 7-1          |

| 2548-1         | Fully Decoded, 2048-Bit Random Access Memory                   | MOS                          | 7-1<br>7-5   |

| 2602           | Fully Decoded, 1024-Bit Static Random Access                   | MOS                          | 7-5<br>7-12  |

|                | Memory                                                         |                              | 7-12         |

| MULTIPLEXERS   |                                                                |                              |              |

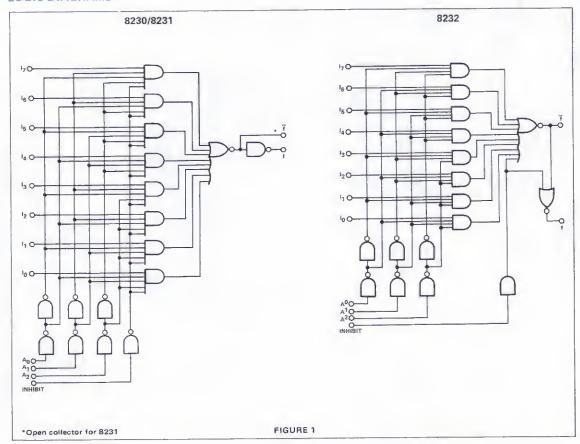

| 8230           | 8-Input Digital Multiplexer                                    | MCI/TTI COCC                 |              |

| 8231           | 8-Input Digital Multiplexer                                    | MSI/TTL 8000                 | 3-17         |

| 8232           | 8-Input Digital Multiplexer                                    | MSI/TTL 8000                 | 3-17         |

| 8233           | 2-Input 4-Bit Digital Multiplexer                              | MSI/TTL 8000                 | 3-17         |

| 8234           | 2-Input 4-Bit Digital Multiplexer                              | MSI/TTL 8000                 | 3-23         |

| 8235           | 2-Input 4-Bit Digital Multiplexer                              | MSI/TTL 8000                 | 3-23         |

| 8266           | 2-Input 4-Bit Digital Multiplexer                              | MSI/TTL 8000                 | 3-23         |

| 8267           | 2-Input 4-Bit Digital Multiplexer                              | MSI/TTL 8000                 | 3-23         |

|                |                                                                | MSI/TTL 8000                 | 3-23         |

| PHASE LOCKED L |                                                                |                              |              |

| PLL            | Phase Locked Loop Introduction                                 | Linear                       | 6-1          |

| PLL            | Terminology                                                    | Linear                       | 6-3          |

| PLL            | Principle                                                      | Linear                       | 6-5          |

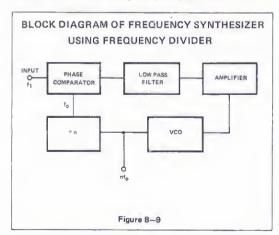

| PLL            | Building Blocks                                                | Linear                       | 6-9          |

| PLL<br>PLL     | Functional Applications                                        | Linear                       | 6-12         |

| PLL            | General Loop Setup and Tradeoffs                               | Linear                       | 6-15         |

| PLL            | Measurement Techniques                                         | Linear                       | 6-18         |

| PLL            | Monolithic Phase Locked Loops                                  | Linear                       | 6-22         |

| PLL            | Expanding Loop Capability                                      | Linear                       | 6-34         |

| PLL            | FM IF Amplifier/Demodulator with Muting                        | Linear                       | 6-41         |

| PLL            | FM Demodulator                                                 | Linear                       | 6-41         |

| PLL            | AM Receiver                                                    | Linear                       | 6-43         |

| PLL            | IF Stage with AGC and AM/FM Detection                          | Linear                       | 6-44         |

| PLL            | Translation Loop for Precise FM FSK Demodulators               | Linear                       | 6-45         |

| PLL            | Analog Light-Coupled Isolators                                 | Linear                       | 6-46         |

| PLL            | Phase Modulators                                               | Linear                       | 6-48         |

| PLL            | Dual Tone Decoders                                             | Linear                       | 6-49         |

| PLL            | High Speed, Narrow Band Tone Decoder                           | Linear                       | 6-49         |

| PLL            | Touch-Tone® Decoder                                            | Linear                       | 6-49         |

| PLL            | Low Cost Frequency Indicator                                   | Linear                       | 6-50         |

| PLL            | Crystal Stabilized                                             | Linear                       | 6-51         |

| PLL            | Ramp Generators                                                | Linear                       | 6-51         |

| PLL            | Sawtooth and Pulse Generators                                  | Linear<br>Linear             | 6-52         |

| PLL            | Triangle-to-Sine Converters                                    | Linear                       | 6-52         |

| PLL            | Single Tone Burst Generator                                    |                              | 6-53         |

| PLL            | Low Frequency FM Generators                                    | Linear<br>Linear             | 6-54         |

| PLL            | RF-FM Generators                                               |                              | 6-54         |

| PLL            | Precision Power Inverter                                       | Linear<br>Linear             | 6-54         |

| PLL            | Design Ideas                                                   |                              | 6-55         |

| PLL            | References                                                     | Linear<br>Linear             | 6-55<br>6-66 |

| REGISTERS      |                                                                |                              |              |

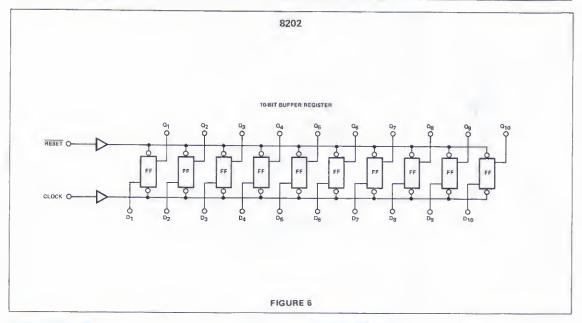

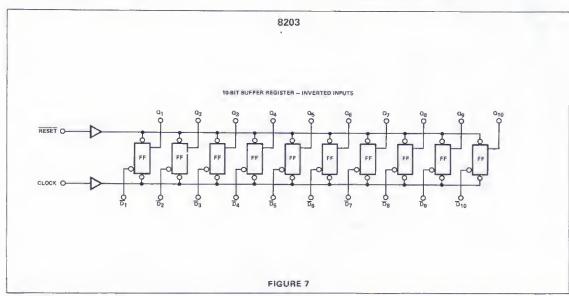

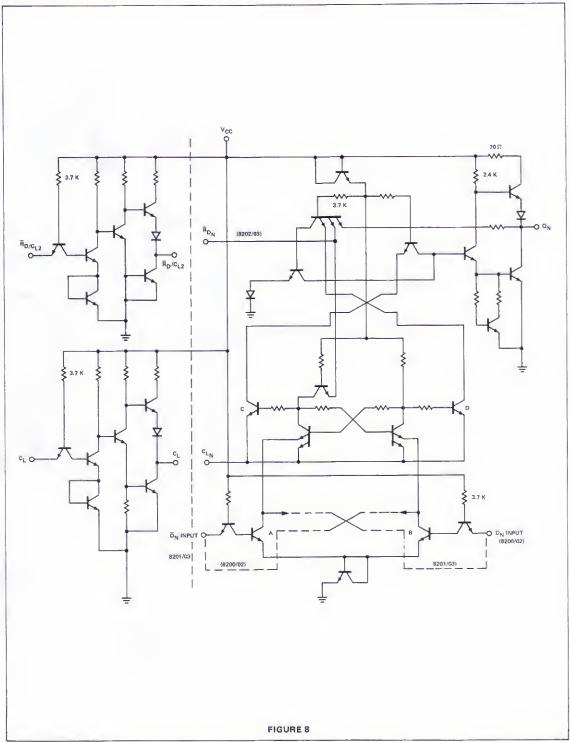

| 8200           | Dual 5-Bit Buffer Register                                     | MCI/TTI 0000                 | 0.4          |

| B201           | Dual 5-Bit Buffer Register with D Complement                   | MSI/TTL 8000                 | 3-1          |

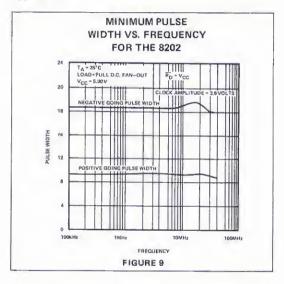

| 8202           | 10-Bit Buffer Register With D Complement                       | MSI/TTL 8000                 | 3-1          |

| 8203           | -                                                              | MSI/TTL 8000                 | 3-1          |

| B243           | 10-Bit Buffer Register with D Complement 8-Bit Position Scaler | MSI/TTL 8000                 | 3-1          |

| B270           | 4-Bit Shift Register                                           | MSI/TTL BOOD                 | 3-36         |

| 8271           | 4-Bit Shift Register                                           | MSI/TTL BOOD                 | 3-1          |

| B276           | 8-Bit Shift Register                                           | MSI/TTL 8000<br>MSI/TTL B000 | 3-1          |

|                | S S. C. C. Frograter                                           | 14131/ 1 1 L DUUU            | 3-1          |

| TIMERS         |                                                                |                              |              |

| 555            | Timer                                                          | Linear                       | 6-79         |

|                |                                                                |                              |              |

# signeties

INTERFACE APPLICATIONS

### 8T00 Interface Functional Index

#### 8TOO INTERFACE

| 8T01                   | Nixie* Decoder/Driver                  | 2-1  |

|------------------------|----------------------------------------|------|

| 8T04/5/6               | Seven Segment Decoder/Driver           | 2-6  |

| 8T09/10                | 8T09 Quad Bus Driver/8T10 Quad D-Type  | 2-16 |

|                        | Bus Flip-Flop                          |      |

| 8T13/14                | 8T13 Line Driver/8T14 Line Receiver    | 2-22 |

| 8T14                   | 8T14 As A Schmitt Trigger              | 2-28 |

| 8T15/16                | 8T15 Line Driver/8T16 Line Receiver    | 2-30 |

| 8T20                   | 8T20 Bi-Directional One-Shot           | 2-36 |

| 8T22                   | Retriggerable Monostable Multivibrator | 2-46 |

| 8T23/24                | 8T23 Line Driver/8T24 Line Receiver    | 2-54 |

| 8T25                   | Dual Sense Amplifier                   | 2-58 |

| 8/26                   | Quad Bus Driver/Receiver               | 2-62 |

| 8T51/54/59/71/74/75/79 | Constant Current LED Drivers           | 2-67 |

| 8T80/8T90/18           | 8T60, 8T90 and 8T18 Interface Elements | 2-71 |

| 8T363                  | Dual Zero-Crossing Detector            | 2-79 |

# DIGITAL 8000 SERIES TTL/MSI

#### DESCRIPTION

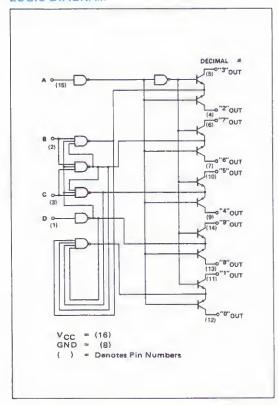

The 8T01 Nixie Decoder/Driver is a one-out-of-ten decoder which has been designed to provide the necessary high voltage characteristics required for driving gas-filled cold-cathode indicator tubes. Typical output breakdown voltages are in excess of 90 volts.

The 8T01 may also be utilized in driving relays or other high voltage interface circuitry. The element is designed with a dielectric isolation process utilizing TTL techniques and is therefore completely compatible with DTL and TTL elements.

The specially designed output drivers have extremely low leakage which eliminates background glow of off cathodes when driving Nixie tubes.

\*Trademark Burroughs Corporation

#### LOGIC DIAGRAM

# MULTIPLEX OPERATION OF NIXIE TUBES USING SIGNETICS' 8TO1 NIXIE DRIVER

Using the Burroughs Nixie Tubes designed for multiplexing techniques, a new approach to readouts can be taken which results in substantial device count savings. Specifically only one decoder/driver will be necessary to drive up to 20 Nixie tubes, though a memory element will be necessary to store the BCD codes, i.e., for 20 tubes one needs 20 four-bit words (assuming that the digits 0 through 9 are to be displayed).

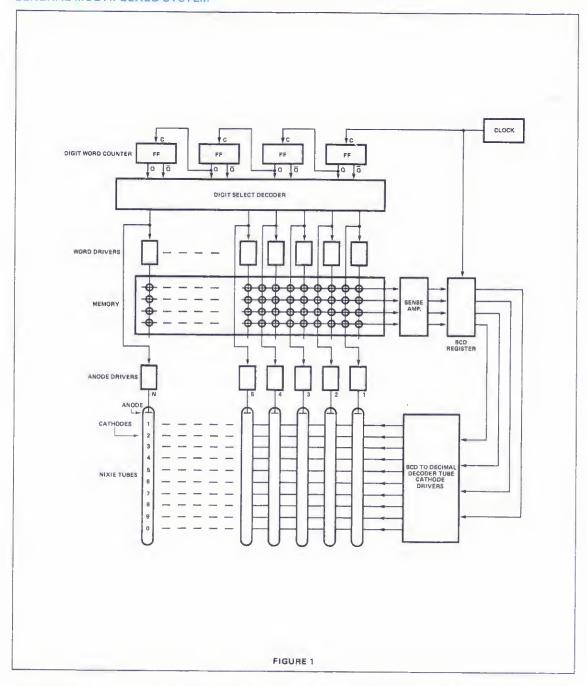

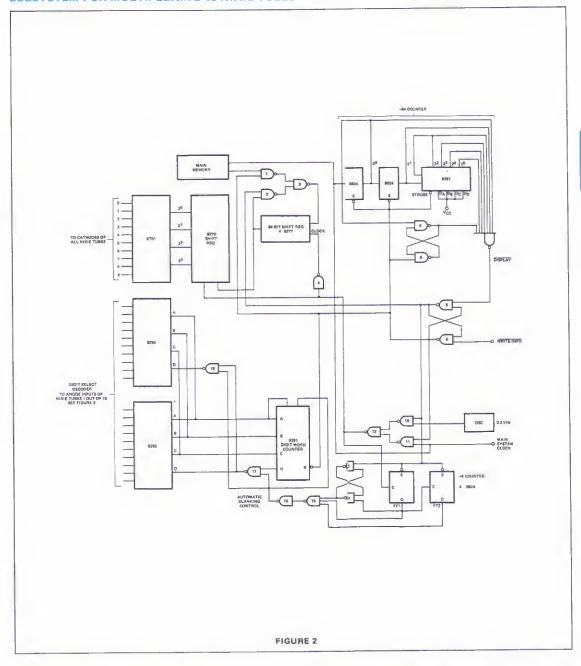

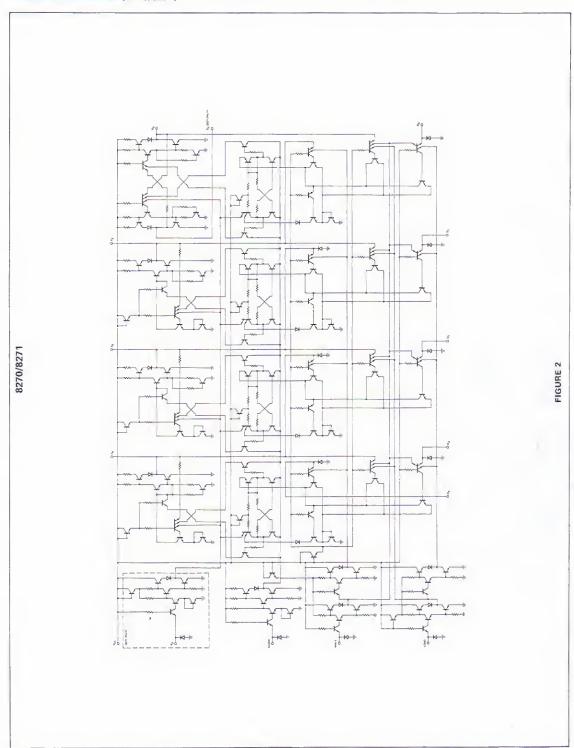

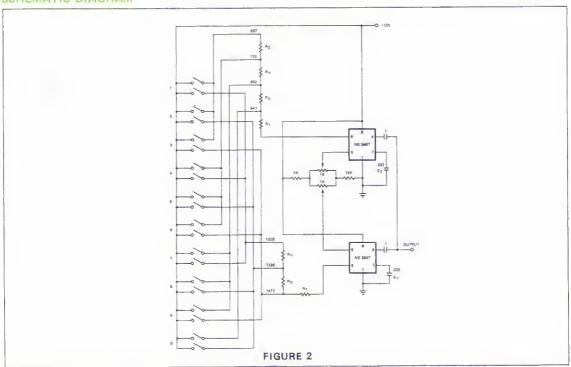

Figure 1 is a block diagram of a logic subsystem for multiplexing Nixie Tubes, This technique can be achieved by combining the 8270 (four-bit shift) registers, 8T01 (Nixie decoder/driver) and 8281 (four-bit binary counter), 8277 (dual 8-bit shift register), in a small subsystem (implementation shown in Fig. 2).

#### TRUTH TABLE

|   | INF | NPUT O |   | OUTPUT |

|---|-----|--------|---|--------|

| D | C   | В      | A | ON     |

| 0 | 0   | 0      | 0 | 0      |

| 0 | 0   | 0      | 1 | 1      |

| 0 | 0   | 1      | 0 | 2      |

| 0 | 0   | 1      | 1 | 3      |

| 0 | 1   | 0      | 0 | 4      |

| 0 | 1   | 0      | 1 | 5      |

| 0 | 1   | 1      | 0 | 6      |

| 0 | 1   | 1      | 1 | 7      |

| 1 | 0   | 0      | 0 | 8      |

| 1 | 0   | 0      | 1 | 9      |

| 1 | 0   | 1      | 0 | 8      |

| 1 | 0   | 1      | 1 | 9      |

| 1 | 1   | 0      | 0 | 8      |

| 1 | 1   | 0      | 1 | 9      |

| 1 | 1   | 1      | 0 | 8      |

| 1 | 1   | 1      | 1 | 9      |

#### **FUNCTIONAL DESCRIPTION**

Figure 1 is a block diagram of a logic subsystem for multiplexing that recently appeared in an application note by Burroughs Corporation. (See Figure 2 for detailed drawing.) The system has a sequentially addressable word select memory with a capacity of N words where N is also the number of Nixie indicators in the system. Each word consists of at least four bits which represent, in binary form, the number of the corresponding decimal digit. The recirculation loop and the write circuits for the memory are not shown in Figure 1, but they would normally be required.

#### GENERAL MULTIPLEXED SYSTEM

When displaying an N digit number, as illustrated in Figure 1, the N words of the memory are sequentially read out at a constant rate that is determined by the system Clock. Each time a word is read out, it is rewritten in the same position of the Memory, thus the information is preserved. When the

displayed information is to be altered in one or more of the digit positions, the new information is written into the corresponding word position in the memory, just after the existing words are read.

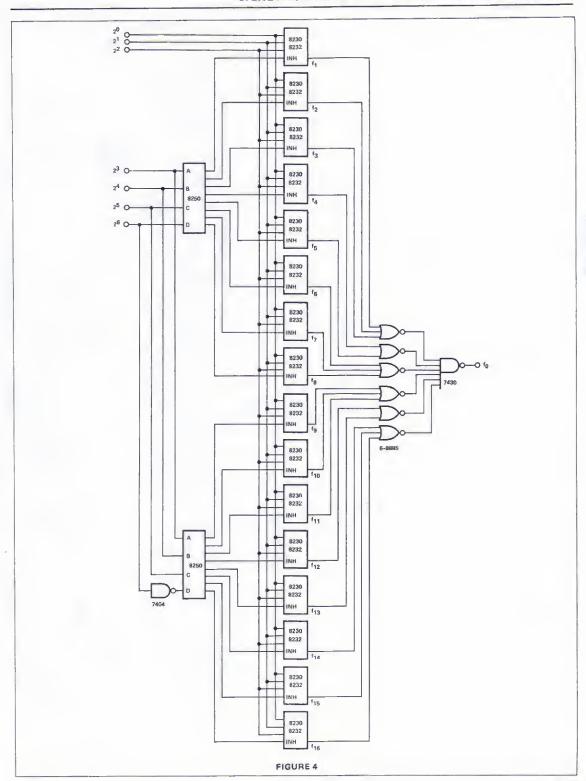

#### SUBSYSTEM FOR MULTIPLEXING 16 NIXIE TUBES

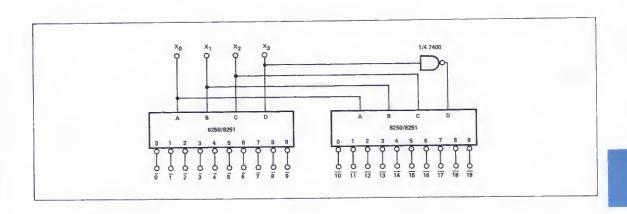

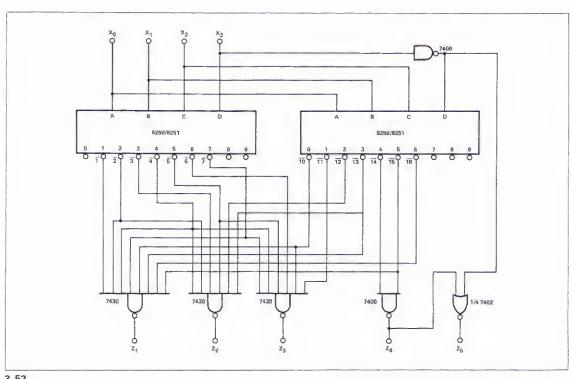

Referring to Figures 1 and 2, four packages of 8277 (dual 8-bit shift register) are used to hold the 16 four-bit BCD coded words that determine what each Nixie tube will display. A four-bit binary counter (8281) is used as the digit word counter. A divide by four counter (2-8822) is used to enable the data after every 4th clock pulse. Two

one-out-freight decoders (8250) are used to implement the digit seect decoder, which drives the appropriate anode througha circuit such as shown in Figure A. The Nixie driver (1701) accepts the four-bit BCD code from memory and drivs the cathodes of the tubes.

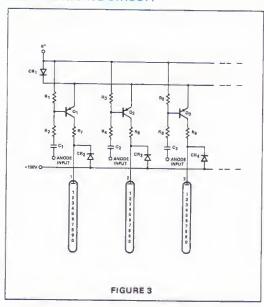

## ANODE DRIVING CIRCUIT

Figure 3 shows a constant voltage anode driver circuit. In the circuit, one of the transistors, Q1, Q2, Q3, etc., is turned on while the others are held off. Diode CR1, in conjunction with the base resistors, R1, R3, R5, serve to back-bias the off transistors. To turn transistor Q1 on, a negative pulse is applied to input number one. The components R2 and C1 are chosen to maintain transistor Q1 in the on condition for the full period required by the system timina.

The collectors of the constant current drivers are connected through catching diodes CR2, CR3, and CR4 to a +100 volt bus. This is done to prevent excessive voltages from appearing across these transistors. Without these diodes. overshoots would tend to occur due to the characteristics of the Nixie tube.

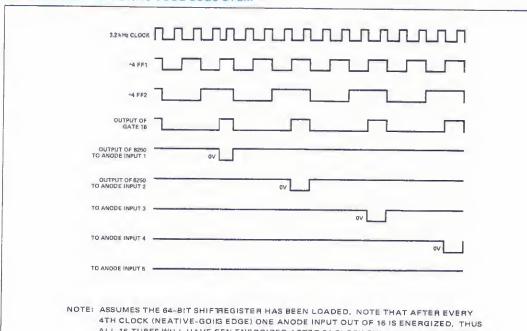

The 3.2kHz oscillator results in a 50Hz signal to an individual anode input. This is sufficiently greater than minimum eye "flicker" frequency (approximately 24Hz.) The upper limit of this oscillator could be 10kHz which will result in a minimum "ON" time of 100 microseconds for each tube. If the main clock repetition rate falls between these limits, there is no need for the oscillator.

### TIMING DIAGRAM FOR 16 TUBE SUBS'STEM

ALL 16 TUBES WILL HAVE EEN ENERGIZED AFTER 64 CLOCK PULSES HAVE OCCURRED.

#### DETAILED DESCRIPTION

Refer to Figure 2 and Figure 3. The 64-bit shift right register is loaded from the main memory with the coded numbers to be displayed by each tube. The operation s as follows:

The write information input (Figure 1) normally logic "1" is set to a logic "0" level (pulsed operation). This allows the words in main memory to be shifted into the register. Also, the main clock from the calculator advances a counter such that after 64 counts the display input is set to logic "0" (pulsed operation), inhibiting any further counter advancement, or loading of the shift register. Simultaneously, as the display input goes to a logic "0", the 3.2kHz oscillator starts cycling the 64-bit shift register. Simultaneously, as the display input goes to a logic "0", the 3.2kHz oscillator starts cycling the 64-bit shift register.

The above is accomplished via the following individual steps:

The latch formed by gates 8 and 9 is initially set such that the output of 8 is a logic "0" level. The output of 8 inhibits the ÷ 4 (divide by four) counter, the 8281 (Digit Word Counter), and conditions the latch formed by gates 13 and 14 such that the output of 14 is set to a logic "0" level. As a result of this action, the output of 16 is a logic "0" level which forces the output of gates 17 and 18 to logic "1" levels.

Logic "1" levels at the "D" input of an 8250 (one out of eight decoder) inhibits the output by forcing them all to logic "1" levels.

At the point in time just prior to the negative-going-edge of the 64th clock pulse, all anode inputs to the NIXIE tubes have been at logic "1" levels. (Logic "1" from the 8250's).

After the 64th pulse (from the main system clock), the  $\div$  64 (divide by 64) counter is decoded and the output of gate 7 goes to logic "0", forcing the latch formed by gates 8 and 9 such that the output of 8 is set to a logic "1" level, thereby releasing the inhibit on the  $\div$  4 and 8281 counters.

Also, all the codes for the digits to be displayed are in the 64 bit shift register and the system is now ready for multiplexing to commence.

Now the system is in the multiplex routine, which is as follows:

The system is clocked by the 3.2kHz oscillator.

The  $\div$  4 counter controls the anode strobing by holding the outputs of the 8250's at logic "1" levels for 4 clock pulses, then allowing one output to make the "1" to "0" transition thus firing the number one NIXIE tube viz. the input capacitor (1 $\mu$ f).

The time constant, TC(1K,  $1\mu f$ ) allows the tube to conduct for approximately 300 microseconds.

The next clock (5th pulse) shuts off the 8251's. When the negative-going-edge of the 8th (eighth) pulse has occurred, then the number 2 NIXIE will be fired. The process repeats for all 16 tubes.

The 8281 (Digit Word Counter) is advanced by the  $\div$  4 counter. Therefore, the 8281 gets advanced *after* the negative-going-edge of every 4th pulse issued by the oscillator.

The outputs of the 8281 are decoded by the 8250's which fire the anodes of the NIXIE tubes.

The 64-bit shift register circulates the 16 BCD coded words that are to be displayed.

The 8270 (4-bit shift register) receives the BCD information from the 64-bit shift register and in turn is decoded by the 8T01 (BCD to Decimal) which drives the cathodes of all 16 tubes simultaneously.

Thus the operation is complete. The automatic blanking control ensures that the tubes are not conducting for 4 shift pulses while the next BCD coded word is shifted into the 8270.

# APPLICATIONS MEMO

8T04 8T05 8T06

DIGITAL 8000 SERIES TTL/MSI

## SEVEN SEGMENT DECODER/DRIVER

#### INTRODUCTION

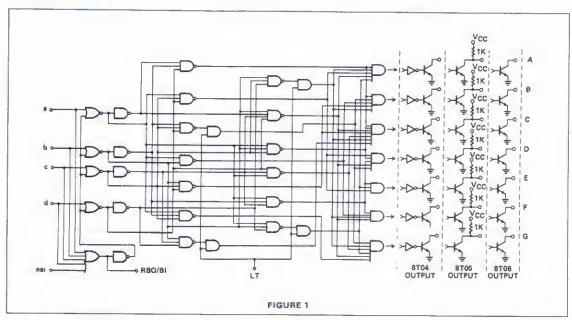

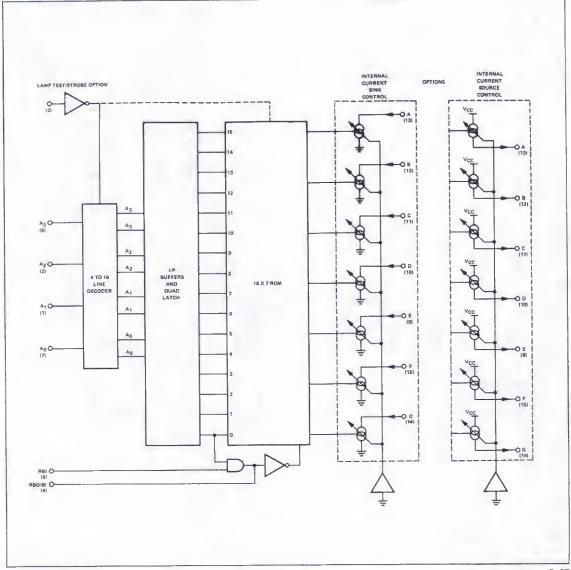

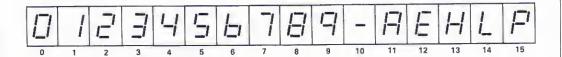

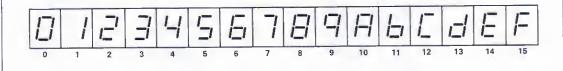

The Signetics' 8T04/5/6 are monolithic MSI seven segment decoder/drivers that have been designed with TTL techniques. They consist of the necessary logic to decode a 4-bit BCD input to provide the appropriate outputs to drive seven segment digital display devices. Numerals 0-9 as well as selected signs and letters can be decoded for driving the following types of displays:

- Light emitting diodes displays (LEDs)

- Incandescent displays

- Interface transistors and SCRs

- Relays

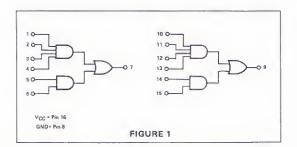

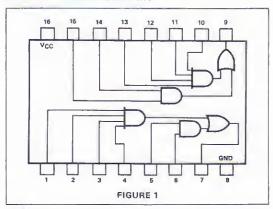

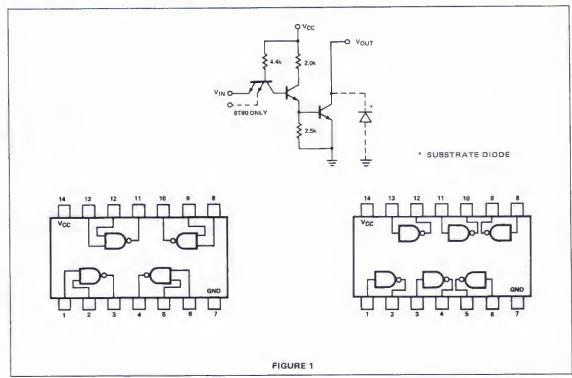

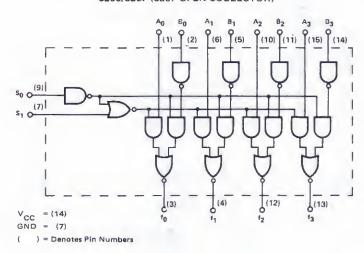

The three decoders differ basically in the electrical characteristics of the output transistors and their logical activating level. Figure 1 shows a composite logic diagram. The 8T04 has "active low," high current sink open collector outputs for driving indicators directly. The 8T05 has "active high" outputs with internal pull-up resistors to provide sufficient drive current to discrete transistors, SCRs and other interface elements as well as Utilogic NOR and OR gates. The 8T06 also offers "active high" outputs but these are of the open collector type for maximum versatility in a variety of current source applications.

#### LOGIC DESCRIPTION

A composite truth table (Table I) has been arranged to show the response of the 8T04/5/6 seven-segment decoder /drivers to a 4-bit binary input code. When neither of the auxiliary inputs are activated, a BCD code on the inputs (a, b, c, d) conditions the outputs (A through G) corresponding to a standard seven-segment layout as shown in Figure 2 such that numerals 0-9 can be displayed. Furthermore, any non-BCD input is defined as well such that selected signs and letters may be displayed in accordance with Table I.

Auxiliary terminals are provided for maximum versatility. A ripple blanking input (RBI) and a ripple blanking output (RBO) are used to suppress leading and trailing edge zeros in multidigit displays. In addition, the internal logic design allows the ripple blanking output to serve as a blanking input as well and is therefore designated as RBO/BI. This blanking input (BI) overrides the ripple blanking signal and may be used in various blanking and intensity modulation applications.

The lamp test (LT) input is independent of any other input and may be activated at any time. This input allows the integrity of the display to be checked by overriding all other input states.

#### LOGIC DIAGRAM

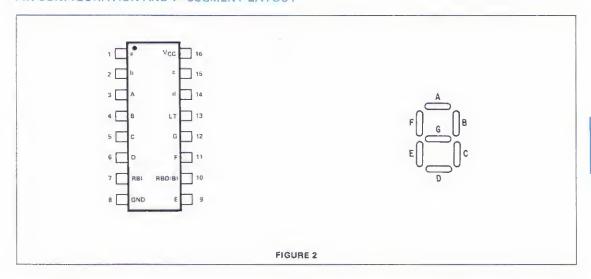

### PIN CONFIGURATION AND 7-SEGMENT LAYOUT

Where: a, b, c, d are the BCD inputs to the decoder/driver A, B, C, D, E, F, G are the seven-segment outputs in accordance with the standard layout as shown.

RBI = Ripple Blanking Input RBO/BI = Ripple Blanking Output/Blanking Input LT = Lamp Test

#### TRUTH TABLE

TABLE 1

| DISPLAY  | /06 | 8T05 | TS I  | UTPU  | 0   |   |   |   | BT04 | S   | TPUT  | ou   |   |   | BI/RBO           |     | UTS       | INP |      |     |    |

|----------|-----|------|-------|-------|-----|---|---|---|------|-----|-------|------|---|---|------------------|-----|-----------|-----|------|-----|----|

| CHARACTE |     | E    | STATI | PUT : | OUT |   |   |   |      | ATE | UT ST | OUTP | ( |   |                  | RBI | LAMP TEST |     | CODE | PUT | IN |

|          | G   | F    | E     | D     | С   | В | A | G | F    | E   | D     | С    | В | A | NOTE             |     | LT        | a   | b    | c   | d  |

| 8        | 1   | 1    | 1     | 1     | 1   | 1 | 1 | 0 | 0    | 0   | 0     | 0    | 0 | 0 | ×                | х   | 0         | Х   | х    | Х   | X  |

| BLK      | 0   | 0    | 0     | 0     | 0   | 0 | 0 | 1 | 1    | 1   | -1    | 1    | 1 | 1 | 0<br>Note 1 & 2) | X   | 1         | X   | Х    | X   | X  |

| BLK      | 0   | 0    | 0     | 0     | 0   | 0 | 0 | 1 | 1    | 1   | 1     | 1    | 1 | 1 | 0                | 0   | 1         | 0   | 0    | 0   | 0  |

| 0        | 0   | 1    | 1     | 1     | 1   | 1 | 1 | 1 | 0    | 0   | 0     | 0    | 0 | 0 | (Note 2)         | 1   | 1         | 0   | 0    | 0   | 0  |

| 1        | 0   | 0    | 0     | 0     | 1   | 1 | 0 | 1 | 1    | 1   | 1     | 0    | 0 | 1 | 1                | ×   | 1 1       | 1   | 0    | 0   | 0  |

| 2        | 1   | 0    | 1     | 1     | 0   | 1 | 1 | 0 | 1    | 0   | 0     | 1    | 0 | 0 | 1 1              | ×   | 1         | 0   | 1    | 0   | 0  |

| 3        | 1   | 0    | 0     | 1     | 1   | 1 | 1 | 0 | 1    | 1   | 0     | 0    | 0 | 0 | 1 1              | x   | 1         | 1   | 1    | 0   | 0  |

| Ų        | 1   | 1    | 0     | 0     | 1   | 1 | 0 | 0 | 0    | 1   | 1     | 0    | 0 | 1 | 1                | ×   | 1         | 0   | 0    | 1   | O- |

| 5        | 1   | 1    | 0     | 1     | 1   | 0 | 1 | 0 | 0    | 1   | 0     | 0    | 1 | 0 | 1                | X   | 1         | 1   | 0    | 1   | 0  |

| Ь .      | 1   | 1    | 1     | 1     | 1   | 0 | 0 | 0 | 0    | 0   | 0     | 0    | 1 | 1 | 1                | X   | 1         | 0   | 1    | 1   | 0  |

| 7        | 0   | 0    | 0     | 0     | 1   | 1 | 1 | 1 | 1    | 1   | 1     | 0    | 0 | 0 | 1                | X   | 1         | 1   | 1    | 1   | 0  |

| 8        | 1   | 1    | 1     | 1     | 1   | 1 | 1 | 0 | 0    | 0   | 0     | 0    | 0 | 0 | 1                | X   | 1         | 0   | 0    | 0   | 1  |

| 9        | 1   | 1    | 0     | 0     | 1   | 1 | 1 | 0 | 0    | 1   | 1     | 0    | 0 | 0 | 1                | X   | 1         | 1   | 0    | 0   | 1  |

|          | 1   | 0    | 0     | 0     | 0   | 0 | 0 | 0 | 1    | 1   | 1     | 1    | 1 | 1 | 1                | ×   | 1 1       | 0   | 1    | 0   | 1  |

| BLK      | 0   | 0    | 0     | 0     | 0   | 0 | 0 | 1 | 1    | 1   | 1     | 1    | 1 | 1 | 1                | X   | 1 1       | 1   | 1    | 0   | 1  |

| 8        | 1   | 1    | 1     | 0     | 1   | 1 | 1 | 0 | 0    | 0   | 1     | 0    | 0 | 0 | 1                | ×   | 1         | 0   | 0    | 1   | 1  |

| 1*       | 0   | 0    | 0     | 0     | 1   | 0 | 0 | 1 | 1    | 1   | 1     | 0    | 1 | 1 | 1                | X   | 1         | 1   | 0    | 1   | 1  |

| L        | 0   | 1    | 1     | 1     | 0   | 0 | 0 | 1 | 0    | 0   | 0     | 1    | 1 | 1 | 1                | Х   | 1         | 0   | 1    | 1   | 1  |

| BLK      | 0   | 0    | 0     | 0     | 0   | 0 | 0 | 1 | 1    | 1   | 1     | 1    | 1 | 1 | 1                | X   | 1         | 1   | 1    | 1   | 1  |

#### NOTE:

- 1, RBO/BI used as input

- 2. RBO/Bi should not be forced high when a, b, c, d, RBI terminals are low, or damage may occur to the unit,

- 3. \* Comma

- 4. X = Do not care, either "1" or "0"

#### TERMINAL CHARACTERISTICS

Since these 7-segment decoder/drivers are useful in many applications and interfacing situations involving bipolar as well as MOS circuits, it is important to have a complete understanding of the 8T04/5/6 characteristics.

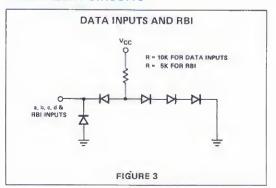

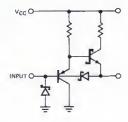

The data inputs as well as the RBI input are TTL type base-emitter diodes. Clamp diodes are employed to prevent ringing that may occur on long interconnect lines. The equivalent circuit is shown in Figure 3.

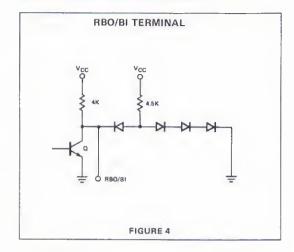

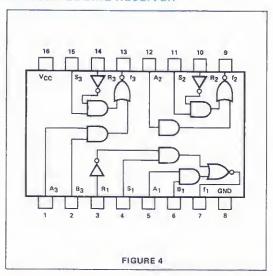

The RBO/BI signal is generated as shown in Figure 4. When a BCD zero has been received at the data inputs with the RBI input being low, transistor Q turns on and the collector pulls the BI input low internally. Since the RBO/BI terminal may be grounded at any time, an overriding blanking signal can be supplied externally. To avoid forcing the collector high when Q is activated, the BI input should be driven by an open collector device such as an 8891.

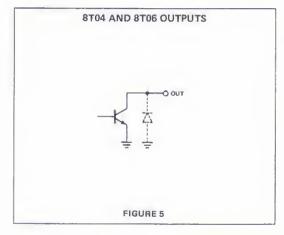

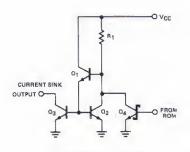

The output transistors of the 8T04 and 8T06 are open collector devices. It can be seen from the equivalent circuit in Figure 5 that because of the collector-substrate isolation diode the output should not be taken more negative than 0.5V without current limiting. The output leakage for the 8T04 and 8T06 is specified at  $100\mu\text{A}$  with 6V applied. Because collector breakdown typically occurs above 15V, an application may be considered with output voltages higher than 6V but below breakdown when using a selected device. In that case, current limiting to about 10mA should be employed to avoid excessive power dissipation in the output transistor.

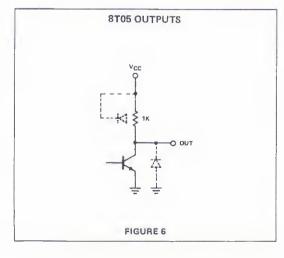

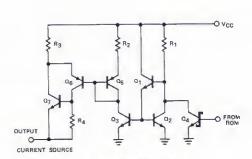

The equivalent circuit for the 8T05 output which has an internal diffused pullup-resistor is shown in Figure 6. In interfacing it should be noted that the output will clamp at one diode drop above VCC.

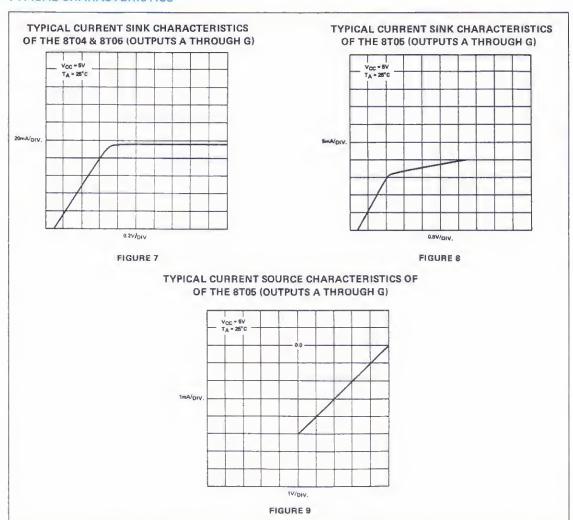

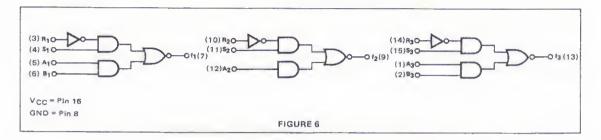

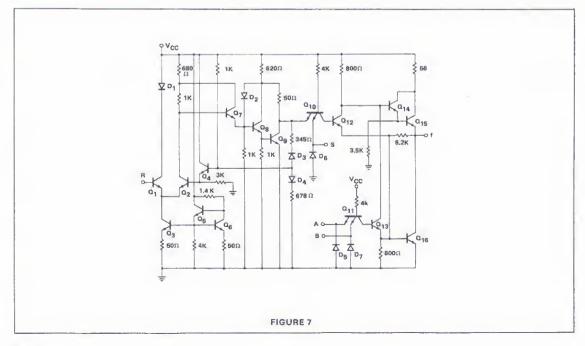

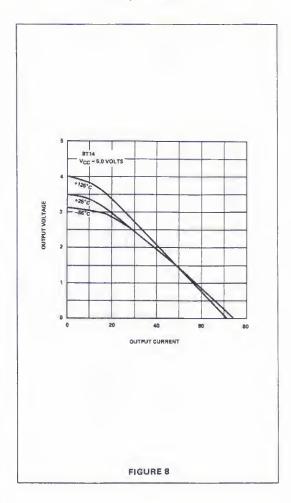

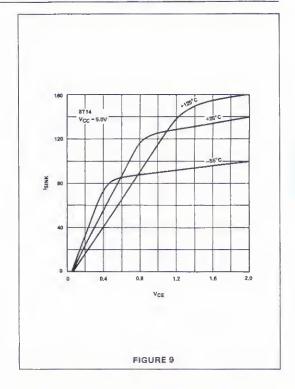

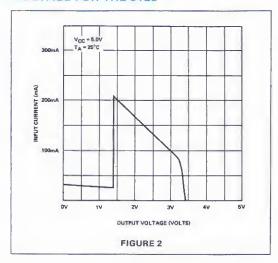

To allow judicious tradeoffs in designs, typical characteristics for current source and sink capability are given for the respective devices in Figures 7 through 9.

#### **EQUIVALENT CIRCUITS**

#### EQUIVALENT CIRCUITS (Cont'd.)

#### TYPICAL CHARACTERISTICS

#### **OUTPUT SPECIFICATIONS**

Table 2 is designed to assist in selecting the proper decoder for a desired application. The 8T04 has "active low" outputs. Thus it is suited for high current sink applications where the driver has to sink current from a load. However,

the 8T05/6 devices have "active high" outputs, meaning that they are well suited for applications where current has to be sourced to the load. This may be done either through the internal pullup resistor (8T05) or through an externally provided element (8T06) when high current is required.

#### OUTPUT SPECIFICATIONS OF THE SEVEN SEGMENT DECODER/DRIVER

| TABLE 2  |                  |                     |                                |                                               |  |  |  |  |

|----------|------------------|---------------------|--------------------------------|-----------------------------------------------|--|--|--|--|

| PART NO. | OUTPUT STRUCTURE | ACTIVATING<br>LEVEL | CURRENT SINK<br>SPECIFICATIONS | OUTPUT "1" LEAKAGE OR<br>CURRENT SOURCE SPEC. |  |  |  |  |

| 8T04     | OPEN COLLECTOR   | LOW                 | 40mA @ .4V                     | 100µA @ 6V                                    |  |  |  |  |

| 8T05     | PASSIVE PULL-UP  | н                   | .5mA @ .3V                     | -2.3mA @ 1V; -500µA @ 3.9 V                   |  |  |  |  |

| 8T06     | OPEN COLLECTOR   | н                   | 40mA @ .4V                     | 100µA @ 6V                                    |  |  |  |  |

#### **APPLICATIONS**

Several techniques are used for driving digital display devices. The most straightforward application is to use one 7-segment decoder/driver for each display. Because a blanking provision is available, the displays may be strobed for low power operation or variable light intensity.

Depending on the existing circuitry it may also be advantageous to time-share one decoder among several or all displays. In such a multiplexed operation, suitable timing and decoding are incorporated such that only one display will be illuminated at a time. This strobed operation is done at a repetition rate high enough to appear flicker free to the eye.

#### LIGHT EMITTING DIODE DISPLAY

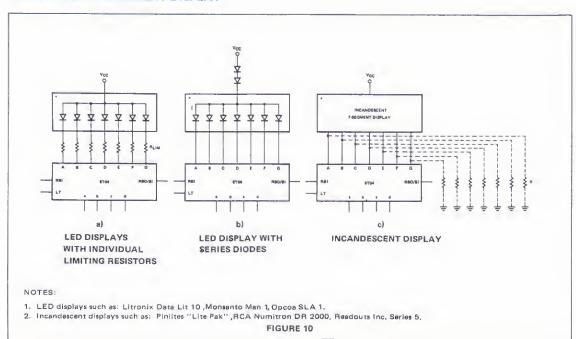

Several light emitting diode displays (LEDs) have common anodes. These require a decoder/driver with "active low" outputs and high current sink capability. Similar requirements exist for incandescent displays and the 8T04 is ideal for these applications without the need for interface transistors.

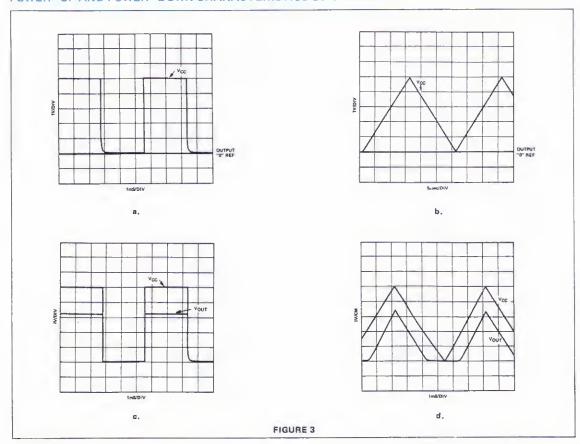

The turn-on characteristics of the display are important when interfacing with the decoder/driver. Figure 10a shows

the 8T04 driving a light emitting diode display. Since the forward drop of the LEDs may be slightly unequal, they may exhibit current-hogging if driven from a common voltage source. Thus, to obtain equal brightness in the display segments, LED manufacturers generally advise to use individual current limiting resistors. However, LED displays have been used successfully without an apparent difference in brightness as shown in Figure 10b. Current limiting resistors are therefore eliminated.

An important consideration for incandescent displays is inrush current through a cold filament, since it could be 10 times as high as the rated operation current. Figure 10c shows the 8T04 driving an incandescent seven-segment display and if the external resistors R (dotted connections) are used, a small current is allowed to flow through the lamps during the off-state, keeping the filaments warm. Thus, inrush current effects are minimized, prolonging the life of the lamp.

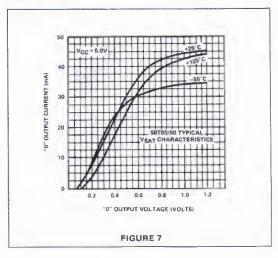

Surge current protection of the driver is not required in this context because the current-sink capability of the output transistors is beta-limited. Typical tests have shown that the output characteristics flaten out at about 80mA (Figure 7), therefore setting a natural limit to inrush current. Consequently, no damage to the driver will be sustained when driving lamps that have steady state currents falling within the defined output drive capability of the seven-segment decoder/driver.

#### 8T04 DRIVING 7-SEGMENT DISPLAY

#### 8T05 INTERFACING APPLICATION

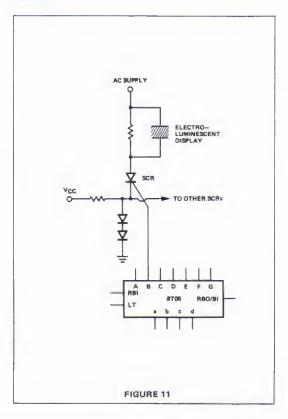

The 8T05 has "active high" outputs with internal 1K ohm pullup such that external buffers may be driven directly without the need for additional components. Hence, it is easy to interface with driver transistors that may be required for very high current incandescent lamps or high voltage interfaces to fluorescent or gas discharge displays.

Should the need exist to interface with logic circuits, one standard TTL load (-1.6mA @ .4V) can be driven. Utilogic OR and NOR gates have base inputs and only require 180µA input current, thus allowing a fanout of 10. The 8T05 can also be used to drive SCR's such as to interface the 7-segment decoder with electroluminescent displays that require high AC voltages. Such an application is shown in Figure 11.

If additional drive current is required from the 8T05 it is possible to add external resistors from V<sub>CC</sub> to the 7-segment outputs of the decoder/driver. Since the minimum value of the total pullup resistors is constrained by

the current sink capability of the output transistors, it is advantageous to use the 8T06 which is pin compatible and designed for high current source applications.

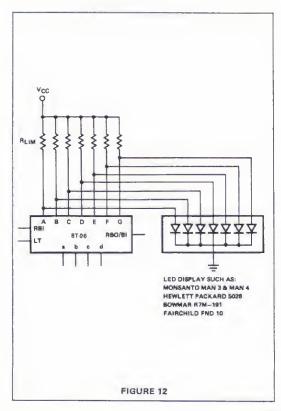

#### LED DISPLAY USING THE 8T06 DRIVER

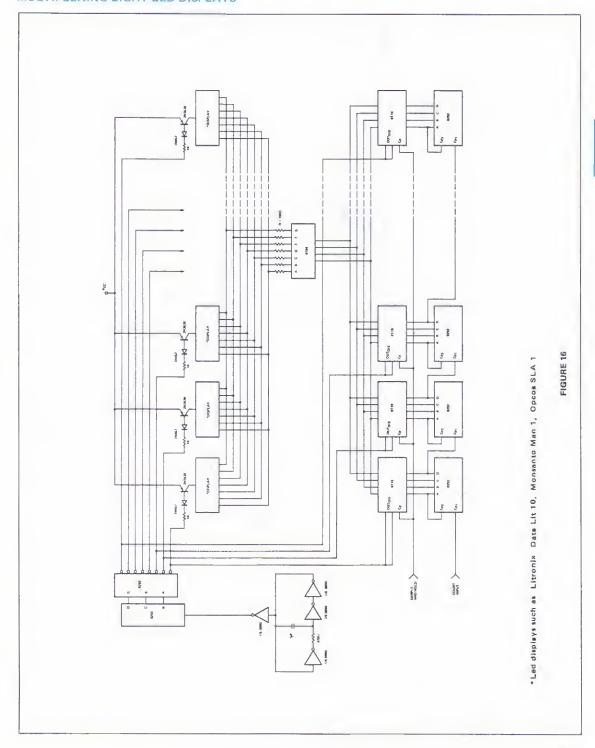

Monolithic light emitting diode displays are presently manufactured with common cathodes which require a driver with current source capability. The 8T06 7-segment decoder/driver has been designed specifically to drive common-cathode LEDs, and employs open-collector transistors for maximum versatility. External pullup resistors must be used to limit the source currents in accordance with the LED manufacturers specifications and the intended usage of the display. A typical application of the 8T06 driving a common cathode LED is shown in Figure 12. Because of the 8T06's high current sink capability (40mA), it can be used as a LED driver for pulsed operation or in the multiplex mode where only one decoder/driver is used for a multidigit display. Figure 16 shows such an arrangement in detail.

# 8T05 DRIVING ELECTRO—LUMINESCENT DISPLAY

#### 8T06 DRIVING MONOLITHIC LED DISPLAY

# RIPPLE BLANKING AND INTENSITY MODULATION APPLICATION

The provision for automatic blanking of leading and/or trailing edge zeros is a very useful feature in multi-digit displays. By blanking insignificant zeros, any display can be easily read. For example, in a ten digit display a mixed integer fraction (000457.1800) would be displayed as 457.18.

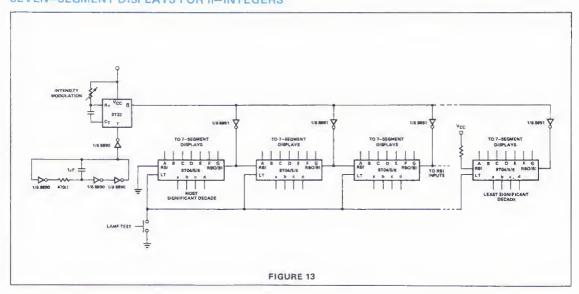

To suppress leading edge zeros, the Ripple Blanking Output (RBO) of a decoder is connected to the Ripple Blanking Input (RBI) of the next lower stage device. In the total display, the most significant bit's RBI input is connected to ground to enable the blanking command to ripple through if that decoder is addressed with a BCD zero (0000). It is common practice to tie the least significant bit's RBI input to VCC since it is generally not desirable to blank the least significant integer. Figure 13 shows an example for n-integers.

Trailing edge zero suppression is needed when the fractional part of a number has to be conditioned similar to the example above. Because it is desirable to retain the first zero after a decimal point, the RBI input of the most significant digit in the fractional part should be tied to VCC.

The RBO terminal may also be used as an overriding blanking input (BI) in a variety of inhibiting and strobing operations that may be associated with the outputs. An extremely useful application also shown in Figure 13 is intensity modulation. The variable duty cycle multivibrator can be used for low duty cycle strobed operation or display dimming.

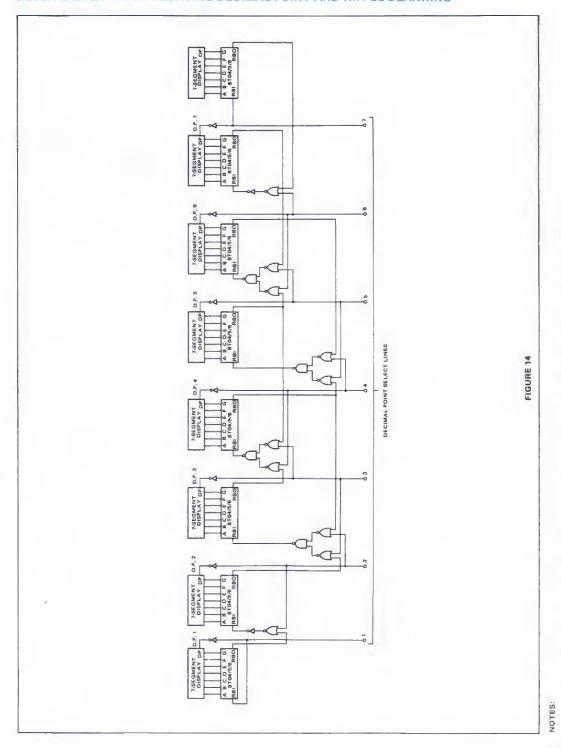

#### FLOATING DECIMAL POINT APPLICATION

The ripple blanking shown in the previous example may be extended to an application such as desk calculator displays where the position of the decimal point can be selected. In Figure 14 a few additional gates are used such that the decimal point can be fixed by means of a "select line". To select the decimal point position, the corresponding select line must be at a logical "1" while all the other select lines are held at a logical "0".

As a result, the least significant integer as well as the most significant part of the fraction will not be blanked (since 0.0 may occur which is a meaningful result) but any other leading or trailing edge zero will be blanked to obtain an easily readable display.

#### SEVEN-SEGMENT DISPLAYS FOR p-INTEGERS

#### NOTES:

- RIPPLE BLANKING— Automatically suppresses all unnecessary zero's which may be either those preceding the first significant digit

(as shown) or those trailing the last significant digit after a decimal.

- LAMP TEST— Overrides all output states generated from input codes.

- 3. INTENSITY MODULATION:— Turns on the seven-segment displays only for the pulse duration. This may be used as a lamp intensity control or for low duty cycle pulsed operation.

### 8 DIGIT DISPLAY WITH FLOATING DECIMAL POINT AND RIPPLE BLANKING

1. To select a decimal point, the corresponding select line must be at a logical "1" while all the remaining select lines are held at logical "0"s. 2. Gates used: 8880 Cuad 2-Input NAND Gate; 8885 Cuad 2-Input NOR Gate; 8890 Hex Inverter.

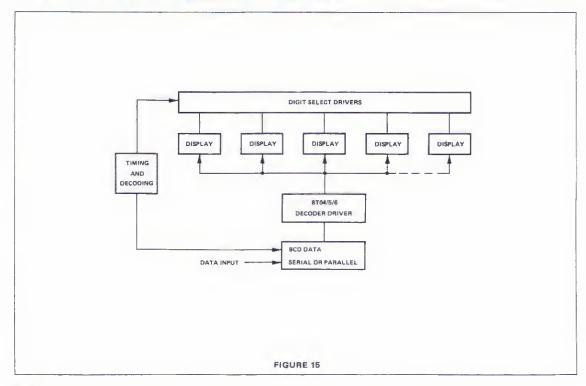

#### MULTIPLEXING OF DISPLAYS

When designing with multidigit displays, two distinctly different approaches may be taken when interfacing the displays with the decoder/driver circuitry. The standard solution would be to use one decoder/driver for each digit in the display. As the number of digits increases it is generally advantageous to time-share one decoder/driver among all digits or groups of digits as shown in Figure 15.

The choice of one technique over the other depends heavily on the application. In particular, the total hardware cost, package count, and power consumption in a multiplexed display system are not only influenced by the number of digits that time share a decoder/driver, but also if the BCD data is available in serial or parallel form.

The principal argument that may be advanced for multiplexing of displays is generally one of economics although a considerable power savings may result as an added benefit. For example, LED 7-segment displays have a high persistence allowing them to be strobed with a very low duty cycle which is an important consideration for battery powered equipment.

A circuit for multiplexing a counter display is shown in Fig.16. By using the 3T10 Quad-D-Type Bus Flip-Flop with tri-state outputs, for storage buffers, the digit information of all counter outputs can be bussed onto common BCD lines. Thus, the design of a multiplexed display is greatly simplified. In this example, common anode displays are driven by an 8T04. Current limiting resistors are used in each 7-segment line to assure equal brightness even if the LED turn-on voltages are slightly unequal.

The 8250 Octal decoder that selects the BCD information from 8T10 buffers and corresponding digit drivers is indexed by an 8293 counter in the divide-by-8 mode. A 1kHz repetition rate for the multiplex oscillator was chosen which is high enough to make the display appear flicker free to the eye.

Notice that the 8T04 and 8T06 are very well suited for strobed operation of displays. Because of their high current sink capability, displays can be pulsed with high currents and low duty cycles, enhancing the apparent brightness of the displays and saving power at the same time. Use of the 8292 and 8293 counters further reduces system power consumption.

#### GENERALIZED MULTIPLEXING SCHEME FOR DISPLAYS

### MULTIPLEXING EIGHT LED DISPLAYS

8T09 8T10

DIGITAL 8000 SERIES TTL/MSI

# 8T09 QUAD BUS DRIVER/8T10 QUAD D-TYPE BUS FLIP-FLOP

#### INTRODUCTION

Designers of digital systems have been using open-collector TTL logic for many years because its wire-OR capability is a powerful design tool. With the addition of an external pull-up resistor, many open-collector outputs can be connected onto a common bus, resulting in a considerable savings of hardware and speed advantages over conventional approaches. Particularly in computer design where busorganized systems architecture prevails, Signetics open-collector MSI and open-collector gates are used extensively.\* There are applications, however, especially in systems with electrically short interconnects, such as oncard bussing and areas of modular systems design, in which performance can be improved by two new TTL compatible bus driver circuits that have been developed by Signetics.

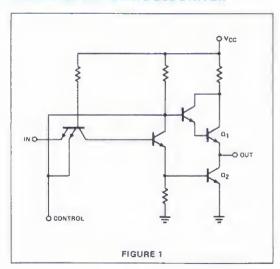

SIMPLIFIED TRI-STATE BUS DRIVER

These designs, the 8T09 Quad Bus Driver and the 8T10 Quad D-Type Flip-Flop combine the advantages of active pull-up TTL with the wire-OR capability of open-collector I Cs. As shown in the simplified circuit diagram in Figure 1, a bus driver can be designed to exhibit three distinct output states. Such a tri-state device is unique in that it may act as a normal TTL gate with low impedance logical "1" and logical "0" levels as long as the control line is high. If the

\*Unified Bus Maximizes Minicomputer Flexibility, ELEC-TRONICS, December 21, 1970. control line is grounded, drive current is removed from the active pull-up Darlington-structure and a third, high impedance output state results. Since in that third state both output transistors ( $Q_1$  and  $Q_2$ ) are biased in the off-condition, only microampere leakage current will have to be supplied to the device by an active bus driver tied to the same bus.

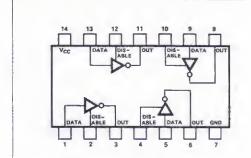

Two integrated circuits, the 8T09 Quad Bus Driver and the 8T10 Quad D-Type Bus Flip-Flop that have tri-state outputs will be described here and applications such as bus organized information transfer, modular systems design and multiplexing will be discussed.

#### 8T09 QUAD BUS DRIVER

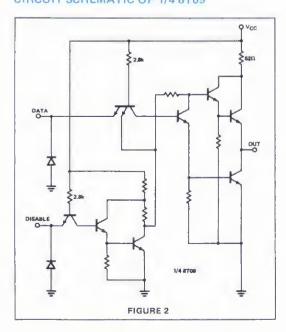

The 8T09 Quad Bus Driver is a hardware realization of the tri-state bus driver concept. It may be seen from the circuit diagram in Figure 2 that depending on the state of the disable input, a driver will either act as a high speed inverting buffer or will exhibit a high impedance "OFF" state similar to an open-collector gate.

#### CIRCUIT SCHEMATIC OF 1/4 8T09

The Darlington pull-up structure at the output provides high current source capability (guaranteed 5.2mA at 2.4V) when driving a data bus, thus allowing high speed operation even when driving heavy capacitive loads. The current sink capability of the bottom transistor is 2-1/2 times that of a standard TTL gate (guaranteed 40mA at 0.4V) making the device very versatile in a variety of interface situations.

Figure 3 shows the logic diagram and truth table of the 8T09. A logical "0" on the disable input makes the bus-driver a high speed inverting buffer with low impedance logical "1" and logical "0" states. To place the output in the high-Z disable state, the disable signal has to be a logical

"1". This fact is beneficial when considering fail-safe operation since removal of the disable signal, which may happen accidentally, will not damage any driver. The inputs of the 8T09s are diode clamped to discriminate against negative ringing.

# APPLICATIONS OF THE 8T09 QUAD BUS DRIVER

Tri-state outputs combined with high-speed and high output current capability in both the logical "1" and logical "0" level allow the 8T09 to be used in a variety of bus-organized systems and wired-OR applications.

#### LOGIC DIAGRAM AND TRUTH TABLE OF THE 8T09

| DATA | DISABLE | OUTPUT |

|------|---------|--------|

| 0    | 0       | 1      |

| 1    | 0       | 0      |

| 0    | 1       | HI-Z   |

| 1    | 1       | HI-Z   |

FIGURE 3

In existing logic designs, the 8T09 may be used to replace open-collector devices to increase systems speed by as much as a factor of ten. This speed improvement is accomplished by the short propagation delays associated with the data path (10ns max.) and the excellent capacitive drive capability of the 8T09. As an added benefit, pull-up resistors are no longer necessary, which will also have an impact on new systems designs where bussing can be used.

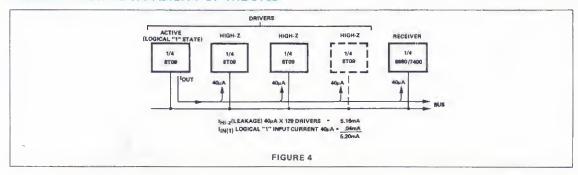

Figure 4 illustrates the excellent drive capability of the 8T09. Since a disabled bus-driver is in the high-Z state and

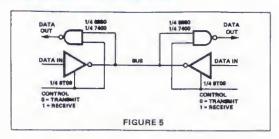

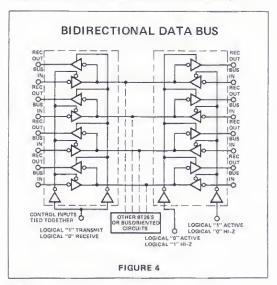

only requires 40uA leakage current, as many as 129 disabled drivers and a standard TTL gate (8880 or 7400)can be driven by one 8T09 in the logical "1" state. The 8T09 also has high current sink capability in the logical "0" state, making many other driver and receiver combinations possible. Of special interest is a bidirectional data bus as indicated in Figure 5. When using standard TTL gates as receivers such as 8880s and 7400s, as many as 25 receiver/transmitter pairs may be tied onto the same bus without exceeding the logical "0" drive capability of the 8T09.

#### LOGICAL "1" DRIVE CAPABILITY OF THE 8T09

#### BIDIRECTIONAL DATA BUS

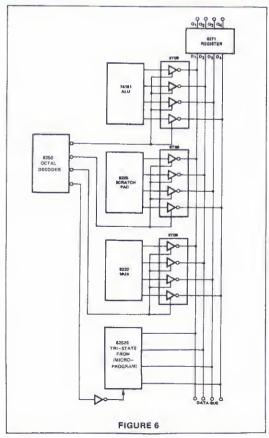

Standard MSI circuits may be adapted easily to busorganized systems. By using the 8T09 as shown in Figure 6, a minicomputer can be designed using a single high speed bus. An arithmetic logic unit (74181), scratch pad memory (8225) and I/O devices (through 8233 multiplexers) may communicate directly. Moreover, microprogrammed instructions from a 1024 bit tri-state FROM (8229) may be put on the bus without need for an interface.

#### 8T09 IN A BUS-ORGANIZED MINICOMPUTER

#### 8T10 QUAD D-TYPE BUS FLIP-FLOP

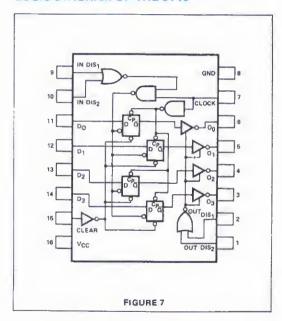

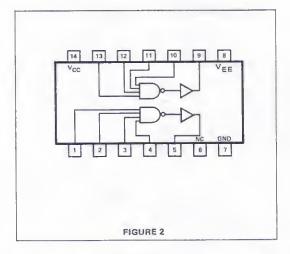

A logical extension of the 8T09 bus driver is the 8T10 Bus Flip-Flop. In one integrated circuit a Quad D-Type flip-flop has been combined with tri-state output drivers for use in bus organized systems. As shown in Figure 7, the outputs are disabled, i.e., switched to the high impedance state when one or both of the inputs to the output disable NOR-gate are a logical "1". Having two output disables facilitates X - Y decoding with active low decoders such as the 8250/51/52. Since the outputs will only be enabled with a logical "0", fail-safe operation in bus-organized systems is assured should the disable signal be removed such as is the case when the disable driver card is removed for some reason.

#### LOGIC DIAGRAM OF THE 8T10

All four D-Type flip-flops operate from a common clock, and the data is transferred from the input to the output on the low-to-high transition of the clock pulse. The minimum clock-pulse width is 12ns.

With one or both of the input disable inputs at a logical "1" the flip-flops are in the hold mode and will store the information clocked in prior to the disable signal. The disable lines may change while the clock is high or low without altering the data. A common clear input has also been provided. All flip-flops will be reset upon application of a logical "1" clear pulse at least 15ns wide.

#### TRUTH TABLE OF THE 8T10

| Dn | INDIS | OUTDIS | ΟUΤ <sub>π+1</sub> |

|----|-------|--------|--------------------|

| 0  | 0     | 0      | 0                  |

| 1  | 0     | 0      | 1                  |

| ×  | 1     | 0      | OUTn               |

| Х  | ×     | 1      | HIGH Z             |

FIGURE 8

The "1" level output current from the 8T10 tri-state outputs is the same as the 8T09, thus by the same argument , an 8T10 output can drive 129 8T10s or 8T09s in the high-Z state as well as a standard 8800 or 7400 gate (Ref. Figure 4). The 8T10 outputs have 32mA current sink capability at 0.4V, meaning that up to 20 standard loads

can be driven. Therefore, like the 8T09, the 8T10 can be used in a variety of applications where high current sink capability is required. To guarantee trouble-free systems performance, all data and control inputs of the 8T10 are diode clamped to discriminate against negative noise and ringing.

# APPLICATIONS OF THE 8T10 QUAD D-TYPE BUS FLIP-FLOP

The buffered tri-state outputs of the 8T10 allow the device to be used directly with other 8T10s in high speed busorganized systems without the need for interface gates or pull-up resistors. Whenever tri-state bus interfaces without storage are desired, the 8T09 may of course be used. The 8T09 bus driver has the same output characteristics as the 8T10 and with slightly higher current sink capability.

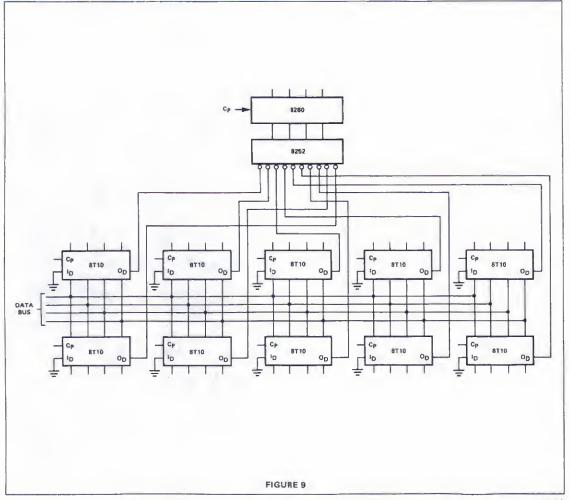

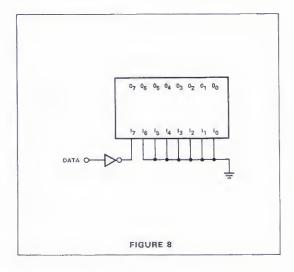

#### MULTIPLEXING OF DATA IN BUS-ORGANIZED SYSTEMS

Multiplexing of data in bus-organized systems is rather simple, as illustrated in Figure 9. Each 8T10 provides data storage and is selected onto the bus by a logical "O" on both output disable lines. By means of an 8252 one-out-of-ten decoder and an 8280 counter, any one of the 10 bus flip-flop devices can be selected. Should another section of the bus be busy, the 8252 may be blanked, which disables all ten 8T10 devices shown.

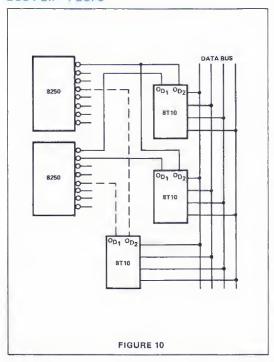

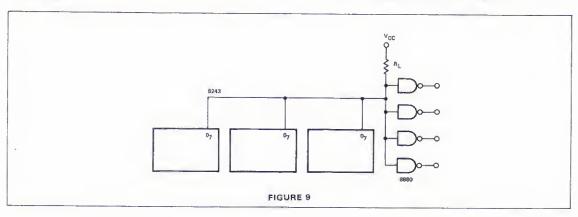

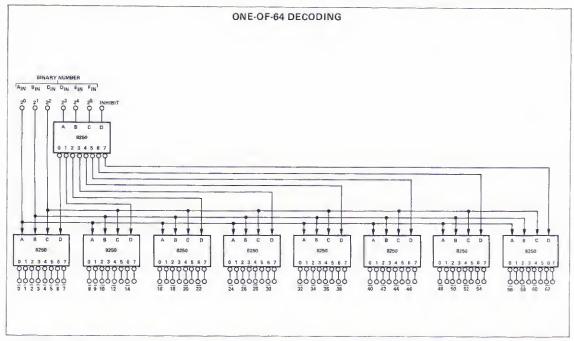

As mentioned previously, as many as 129 other 8T10's, as well as a standard TTL receiving gate may be driven by an enabled 8T10. To facilitate output decoding, each 8T10 has a 2-input NOR-gate for the output disable function. As long as either NOR-gate input is high, the 8T10's outputs will be disabled and in the high-Z state. Figure 10 shows how two 8250 one-out-of-ten decoders are used in an X - Y matrix that can select one-out-of-64 8T10s onto the data bus.

# X-Y MATRIX FOR SELECTION OF 8T10 BUS FLIP-FLOPS

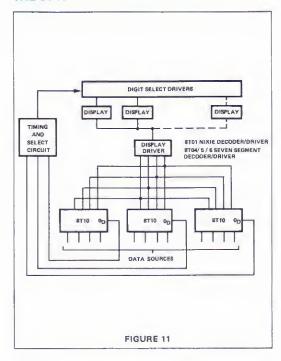

Multiplexing of displays is greatly simplified and hardware is significantly reduced when using the 8T10 Quad D-Type Bus Flip-Flop. Figure 11 shows that one decoder driver such as the 8T01 NIXIE decoder/driver or the 8T04/5/6 seven-segment decoder/driver may be time-shared among several displays. If the display is large enough, the digit select drivers and decoding circuitry will cost much less than individual decoder drivers. In addition, strobing displays will result in a net power savings.

# MULTIPLEXING OF DISPLAYS USING THE 8T10

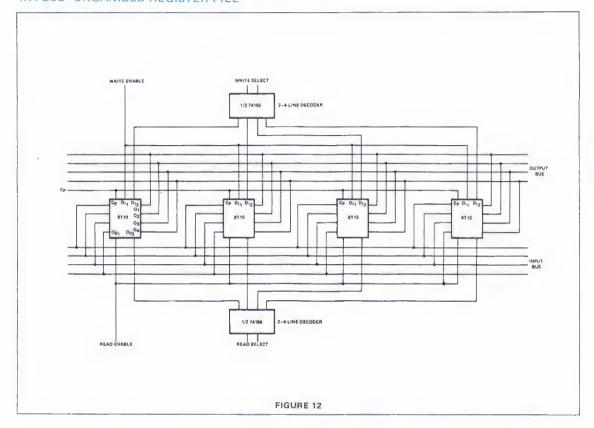

The 8T10 may also be configured into a bus-organized register file that can be used in a variety of applications requiring a scratch pad memory. Figure 12 shows such an application. Simultaneous read and write are possible and the memory is easily expanded in word length. Input and output decoding of the 8T10 is simplified because of its NOR-gate input and output disable lines.

#### SYSTEMS CONSIDERATIONS

The 8T09 and 8T10 bus devices are easy to use but caution should be exercised in systems design with tri-state devices. Because of their high output current capability the 8T09 and the 8T10 should be adequately decoupled just as other TTL drivers, placing a 0.01 to 0.1uf high frequency capacitor as close as possible to the package.

In a system only one tri-state bus device per common bus is allowed to be enabled at a time. It should be realized, however, that in a practical system, control signals may be skewed, creating a slight overlap of the disable signals. Thus it is possible for a transient condition to occur in which two output stages are turned on simultaneously with opposite logic levels. In general, these conditions should be avoided although narrow overlaps of control signals with low duty cycles may not damage any bus drivers and adequate decoupling will handle the surge current demand.

#### 4X4 BUS-ORGANIZED REGISTER FILE

#### DIGITAL 8000 SERIES TTL/MSI

# 8T13 LINE DRIVER/8T14 LINE RECIEVER

#### 8T13 DUAL LINE DRIVER

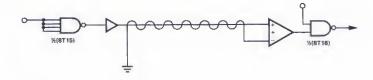

The Signetics 8T13 is primarily intended for driving low impedance transmission lines such as coaxial cable, twisted pair or ribbon conductors. Both input and output are TTL compatible and the device is operated from a single 5 volt power supply.

#### LOGIC

The 8T13 contains two AND-OR circuits with one 4-input and one 2-input AND gate for each driver as shown in Figure 1. Unused inputs should be connected to driven inputs where possible to increase circuit speed and to minimize noise coupling into the device.

### CIRCUIT DESCRIPTION

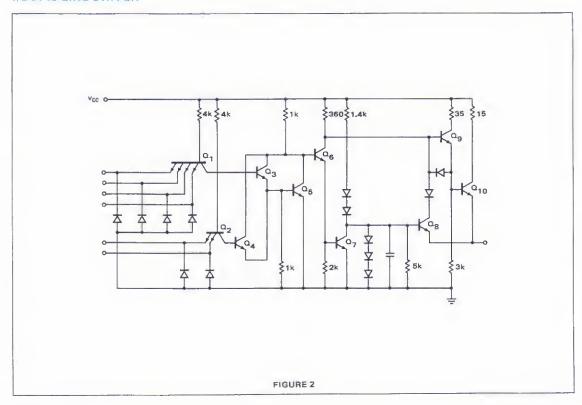

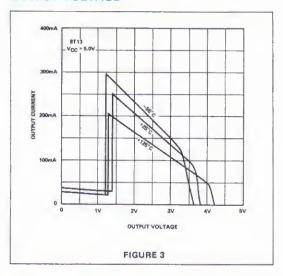

The electrical schematic for one of the drivers is shown in Figure 2. The output of the driver is a low impedance emitter follower with built-in short circuit protection. Referring to the circuit, it can be seen that transistor Qg will turn on once the output has dropped below approximately two diode drops. Base drive will then be diverted from Qg and the output transistor will turn off. Typical output voltage versus current characteristics are shown in Figure 3 over the full temperature range (-55°C to +125°C).

#### 1/2 8T13 LINE DRIVER

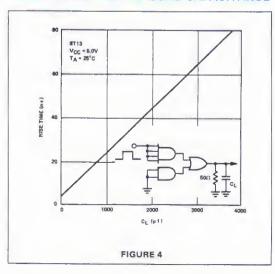

The output impedance of the emitter follower output stage during the logic "0" to logic "1" transition is approximately 15 ohms. This low impedance combined with the inherent drive capability of the 8T13 results in an excellent device for driving heavy capacitive loads. Figure 4 shows the typical rise time versus load capacitance for the 8T13 with a 50 ohm pull-down resistor. The output fall time will be governed by the equation: T=2.2 RC.

Parallel operation of the 8T13 for additional drive capability can be accomplished. The function obtained is then the logic OR of each output tied to the common bus.

# TYPICAL OUTPUT CURRENT VS. CUTPUT VOLTAGE

#### TYPICAL RISE TIME VS. LOAD CAPACITANCE

#### POWER DISSIPATION

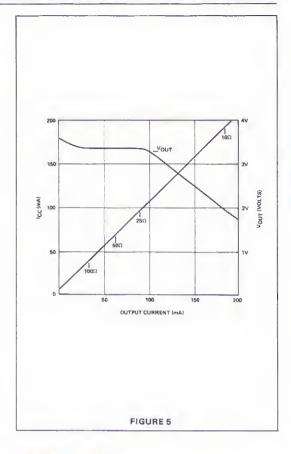

Typical power supply current and output voltage as a function of load current is shown in Figure 5. For convenience corresponding values of load resistance are also shown. This graph is useful in calculating the total power dissipated by both line drivers in a single package.

Depending upon the output state, the power dissipation of each driver is:

For example, if both drivers in a package are connected to 50 ohm lines but one is turned off (logic '0' state), the total power dissipation would be:

$$P_{diss}$$

=  $P_{diss}$  ('1' state) +  $P_{diss}$  ('0' state)

=  $[(5V - 3.3V) \times 65mA] + 190mW$

= 300mW

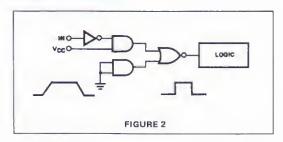

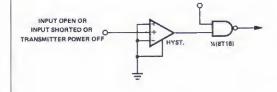

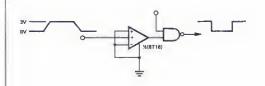

#### 8T14 LINE RECEIVER

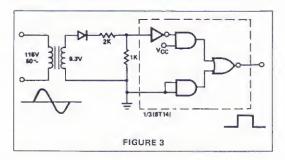

The 8T14 was designed to be used at the receiving end of a transmission line for reshaping digital pulses. The device has a built-in hysteresis of 0.5 volt (typical) to discriminate against line reflections and noise. The line receiver is also TTL compatible and operates from a single 5 volt power supply.

#### LOGIC

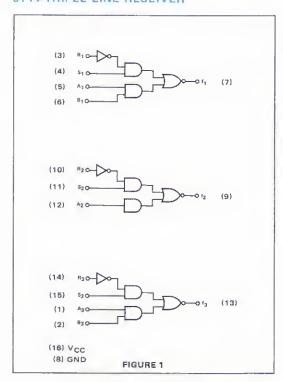

The 8T14 contains three line receivers, each of which can be strobed independently. Additional logic is included to allow the output to be forced to a logic "0" by external control signals. (Refer to Figure 6 for complete logic diagram.)

#### CIRCUIT DESCRIPTION

The receiver input of the 8T14 is basically a differential amplifier with a constant current source replacing the common emitter resistor (see Figure 7). The input impendance is therefore very large, being typically 30-50 kilohms. Loading effects are then minimal, an important

factor when several receivers are used on the same transmission line.

The output of each line receiver is similar to that used in high speed TTL logic gates. Output rise time is reduced with the low impedance Darlington-type pull-up structure. Typical source and sink current capability over the full temperature range are shown in Figures 8 and 9.

#### 1/3 8T14 LINE RECEIVER

#### HYSTERESIS

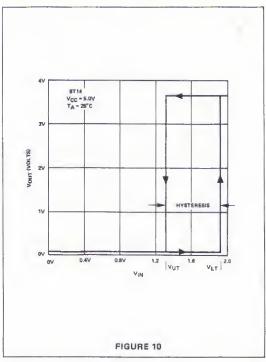

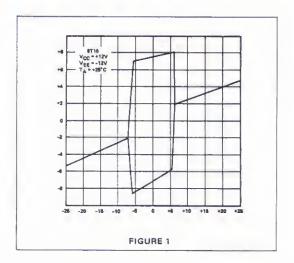

The 8T14 exhibits typically 0.5 volt hysteresis as shown in Figure 10. Using the values of upper and lower threshold voltages as indicated, we can calculate the noise immunity for both logic one and zero levels. These calculations assume that the device is being driven with a logic swing of 0.4 to 2.8 volts.

Logic "1" Noise Immunity (N1)

$$N_1 = V_1 - V_{UT} = 2.8V - 1.35V$$

$$N_1 = 1.45V$$

Logic "0" Noise Immunity (No)

$$N_0 = V_{LT} - V_0 = 1.85V - 0.4V$$

$$N_0 = 1.45V$$

### **APPLICATIONS**

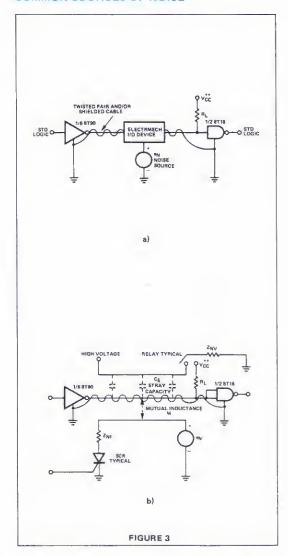

#### TWISTED PAIR

#### PARTY-LINE APPLICATION

## GENERAL EQUATIONS FOR PARTY LINE APPLICATIONS

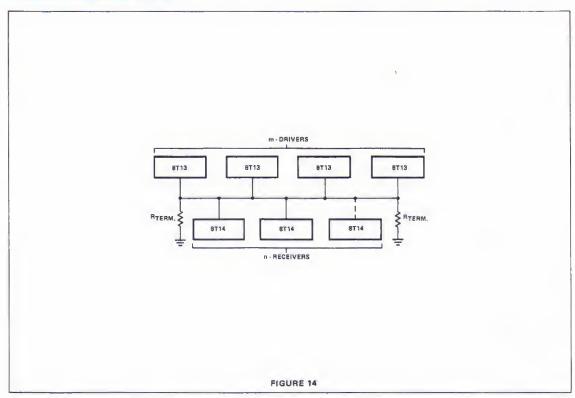

When multiple drivers and receivers are tied onto a common bus in a party-line applications, it can be easily ascertained if the required current is within the drive capability of an 8T13 driver. Figure 14 shows a generalized example.

The equations given below will show if a driver can handle the load.